Kim Seon Deok

[Verilog] Logic status, Data type 본문

Verilog의 논리값

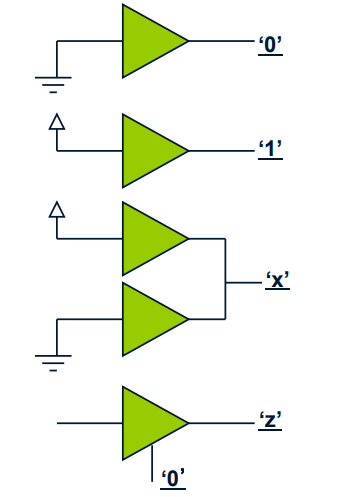

디지털 로직은 크게 4종류의 status를 가질 수 있다.

| 논리 값 | 의미 |

| 0 | 논리 0, false 상태 |

| 1 | 논리 1, true 상태 |

| x | 논리 unknown |

| z | high impedance 상태 |

논리 0은 0V나 조건의 거짓을 의미한다.

논리 1은 Vcc, 전원전압이나 조건의 참을 의미한다.

| 1 | Vih이상 : 논리 1로 인식할 수 있는 높은 전압 |

| unknown | Vil ~ Vih사이 전압 : 논리 unknown로 인식 |

| 0 | Vil 이하 : 논리 0으로 인식할 수 있는 낮은 전압 |

위 그림은 베릴로그의 논리값을 logic으로 표시한 것이다. 위에서부터 0, 1 , x, z이다.

x는 unknown상태로 논리적 충돌이 일어나 해결될 수 없을 때 혹은 don't care를 나타내고

z는 연결이 끊어진 high impedance상태를 나타낸다.

자료형

- net 자료형 : 소자 간 물리적 연결을 추상화한다. → 하드웨어적 특성

논리 게이트. 모듈 등 하드웨어 요소들 사이 물리적 연결을 나타내기 위해 사용한다.

gate primitive, concurrent assign과 같은 driver 값에 의해 net 값이 연속적으로 유지된다.

default 자료형은 1비트의 wire를 뜻하고, default 초깃값은 z이다.

| wire | 단순한 연결 |

| tri | 단순한 연결. HW에서 3상태가 됨. multiple driving sources가 허용됨 |

wire w1, w2 ; // 1 비트 자료형은 선언 생략 가능

wire [7:0] bus // 8 비트 버스

wire enable = 1'b0 ; //enable 자료형은 wire이고 1 비트 이진수 0 을 가짐

tri [15:0] bus // 3상태 16비트 버스| wire / tri | 0 | 1 | x | z |

| 0 | 0 | x | x | 0 |

| 1 | x | 1 | x | 1 |

| x | x | x | x | x |

| z | 0 | 1 | x | z |

- variable 자료형 : 절차형 할당문 사이의 값을 임시로 저장하기 위한 변수이다. → reg, integer, real, time, realtime → 소프트웨어적 특성

procedural assignment의 실행에 의해 값이 바뀌고 할당에서 부터 다음 할당까지 값을 유지한다.

reg, time, integer는 default 초기값이 x이다.

real, realtime은 default 초기값이 0이다.

signed reg / integer / real / realtime → 부호 유지

unsigned reg / integer / real / realtime → unsigned값으로 취급

| reg | procedural assignment에 의해 값을 받는 객체의 자료형 |

| integer | 정수값을 취급, procedural assignment에 의해 값이 변경됨 |

| time | 시뮬레이션 시간을 처리하거나 저장, unsigned 값 |

| real / realtime | 실수형 값을 취급 |

reg a ; // 1비트 reg 자료형

reg [3:0] v; // 4비트 reg 벡터, v[0],v[1],v[2],v[3]으로 구성

reg signed [3:0] signed_reg ; //4 비트

reg [-1:4] b; // 6비트 reg 벡터

reg [4:0] x,y,z // 5비트 reg 벡터 3개

integer a; // integer value

time last_chang ; // time value

real float ; // real value 저장 변수

realtime rtime ; // time을 real value로 저장하는 변수

| 자료형 | 할당모드 | ||||

| gate primitive | concurrent assign | behavioral modeling | assign...deassign PCA |

force...release PCA |

|

| net | Y | Y | N | N | Y |

| variable | comb(N) seq(Y) |

N | Y | Y | Y |

벡터

벡터는 범위 지정 [ msb : lsb ]을 갖는 다중비트의 net 혹은 reg 자료형을 가리킨다.

signed로 선언되거나 signed로 선언된 포트에 연결되는 경우를 제외하고 unsigned로 취급된다.

단일 할당문으로 값을 받을 수 있다.

| 자료형 [ msb : lsb ] 벡터이름 ; |

reg [7:0] ; // 8비트 reg

wire [15:0] d_out ; // 16비트 wire

배열

배열은 reg 또는 wire 를 이용해 선언한다.

배열 전체나 일부분은 단일 할당문에 의해 값을 할당 받을 수 없고 수식에 사용될 수 없다.

RAM, ROM, Register file 등의 메모리 모델링에 사용된다.

| 자료형 배열이름 [ Uarddr : Laddr ] [ Uaddr2 : Laddr2 ] ; | |

| 자료형 [ msb : lsb ] 배열이름 [ Uarddr : Laddr ] [ Uaddr2 : Laddr2 ] ; |

reg [7:0] mema[0:255] /// 8비트 짜리 256개 배열

mema = 0 ; //배열은 값을 할당 받을 수 없다.

mema[0] = 1; // 원소 하나는 값을 할당 받을 수 있다.

reg arrayb[7:0][0:255] ; // 2차원 reg 배열 행 8개 열 256개

arrayb[1][12:31] ; //2차원 배열 중 행 전체도 값을 할당받을 수 없다.

arrayb[1][0] = 5 ; // 원소 하나는 값을 할당 받을 수 있다.

wire w_array[7:0][5:0] // 2차원 wire 배열

integer inta[1:64] // 1차원 64비트 배열 inta

메모리

reg형 요소를 갖는 1차원 배열이다. 메모리 전체가 단일 할당문이므로 값을 할당받을 수 없다.

인덱스로 지정되는 워드 단위로만 값을 할당하거나 수식에 사용 될 수 있다.

reg [1:n] rega ; /// 벡터. n비트 레지스터. n비트 통째로 액세스 가능

reg mema [1:n] ; // 1차원 배열. n개의 1비트 레지스터의 메모리. 한개씩만 액세스 가능

parameter

variable, net 범주에 속하지 않는 상수값이다.

회로의 비트 크기나 지연값을 지정하기 위해 사용된다.

defparam문이나 모듈 인스턴수문의 파라미터 오버라이딩에 의해 값을 변경시킬 수 있다.

parameter msb = 7 ; // msb를 상수 7로 정의

parameter e = 25, f = 9; // e를 25로, f를 9로 정의

parameter [31:0] dec_const = 1'b1; // 1비트 이진수 1을 32비트로 정의

# (정수형 상수)

- 할당문, gate primitive, instance에서는 지연을 뜻함

- 모듈인스턴스 내부에서는 파라미터 값 변경을 의미함

'Verilog' 카테고리의 다른 글

| [Verilog] Gate level modeling (0) | 2022.12.08 |

|---|---|

| [Verilog] Operator (0) | 2022.12.08 |

| [Verilog] 주석, 수 표현 , 문자열, 식별자 (0) | 2022.12.06 |

| [Verilog] Verilog HDL Overview (0) | 2022.12.06 |

| [Verilog] Clock & Testbench & DUT & Reset & Flip Flop (0) | 2022.11.30 |