Kim Seon Deok

[Verilog] Clock & Testbench & DUT & Reset & Flip Flop 본문

Clock

클럭은 펄스신호로 구성된다.

주기(Period) : 기준 시점 이후에 동일한 구간이 나올 때까지 걸린 시간 [Sec]

ex) 처음 rising 에서 다음 rising까지 걸린 시간

주파수(Frequency) : 1초동안 진동한 횟수 [Hz] → Performance에 영향을 미친다.

cpu overclock : 클럭의 동작 주파수를 높일수록 동작 속도가 빨라진다.

1초에 1번 진동이 발생하면 주기는 1초이고 주파수는 1hz이다.

1초에 4번 진동이 발생하면 주기는 1/4(=0.25)초이고 주파수는 4hz

20ns ↔ 50mhz

클럭이 없으면 디지털회로는 동작할 수 없고, 클럭 신호를 기준으로 digital logic이 동기화되어 동작한다.

rising edge : 클럭이 상승할 때 falling edge : 클럭이 하강할 때

`timescale 1ns / 1ps // 1ns : 시간축의 딜레이를 숫자로 표현한 것. delay 단위이다.

// 1ps : 나타낼 수 있는 소수점 정확도. 해상도이다.

module tb_clock_generator;

reg clk;

always // 끊임없이 running

#5 clk = ~clk; // 5ns 단위로 클럭이 반전되며 펄스 신호를 생성

initial begin // 한번만 실행

clk = 0; // 초기 클럭값을 0으로 줌. 0-1-0-1-0-1...반복

#100 // 100ns delay 후에 시뮬레이션 종료

$finish // 시뮬레이션 종료

end

endmodule

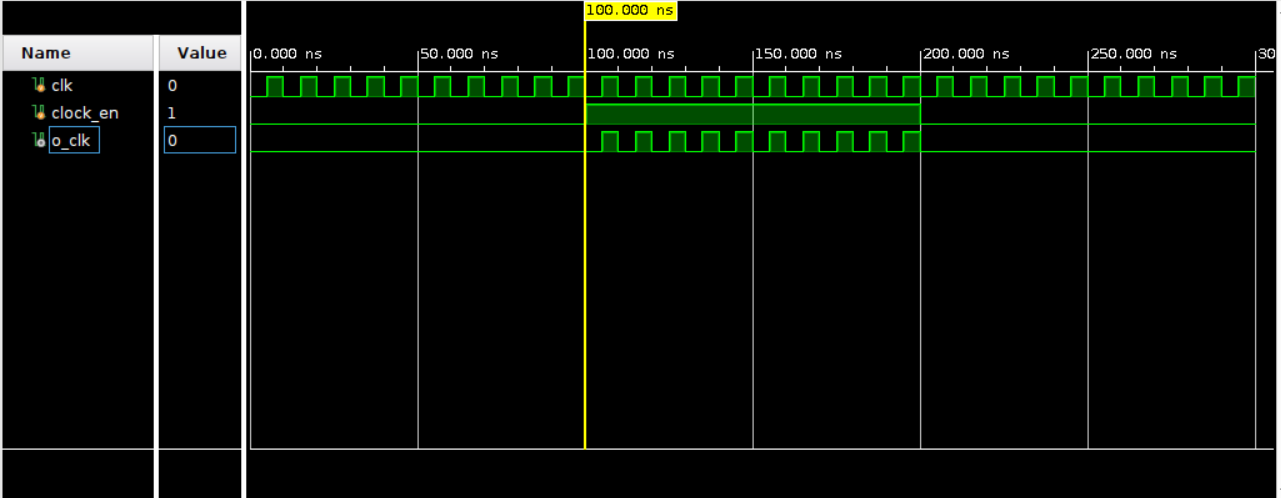

클럭값이 0부터 시작해 5ns단위로 클럭이 0 1 0 1... 반전되고 100ns동안 반전이 유지되는 모습이다.

Testbench

verilog HDL은 하드웨어를 설계할 때에도 사용되지만 설계한 모듈을 검증할 때에도 사용된다.

Testbench는 검증에 사용되는 모듈이고, HW모듈이 아니다.

DUT(Design Under Test)는 우리가 검증하고 싶은 설계한 HW모듈이다.

DUT(Design Under Test)는 Test할 모듈, 즉 검증할 대상을 말한다. testbench 안에 DUT를 배치해 설계한 모듈을 검증

클럭이 enable되면 출력이 클럭과 똑같은 파형으로 출력되고, 클럭 enable되지 않으면 출력은 0이다.

Reset

Reset은 클럭과 마찬가지로 필수적인 역할을 하는 신호이다. 초기화해주는 역할

reset을 사용해야 하는 이유는 logic 의 unknown 상태로 인해 logic의 오동작을 방지하기 위함이다.

디지털 로직이 가질 수 있는 값(value)의 종류

| value | meaning of login level |

| 0 | 0 혹은 조건의 거짓 |

| 1 | 1 혹은 조건의 참 |

| x | unknown |

| z | high impedance |

카르노맵에서 grouping을 많이 할 수록 logic size가 줄어든다. optimize된다.

unknown은 0 또는 1 표현이 둘 다 가능한 상태이다. 즉 don't care상태를 뜻한다.

따라서 x를 사용하면 카르노 맵에서 그룹핑을 더 많이 할 수 있고 logic size가 줄일 수 있다.

플립플롭

1비트의 정보를 보관, 유지할 수 있는 회로. 순차회로의 기본 요소이다. 디지털 로직에서 기본이 되는 저장 로직

이전상태를 계속 유지하여 저장하고 휘발성 메모리이기 때문에 전원공급이 안되면 저장된 내용이 사라진다.

combinational logic : 입력을 가함과 동시에 출력이 바로 나오는 로직 → +, -, and, or 같은 연산용 로직

sequential logic : 이전 상태의 신호와 외부 입력신호에 의해 출력이 결정되는 로직 → 시점에 따라 결과값이 달라지는 로직. 이를 구성하기 위해 저장매체가 필요

디지털 로직에는 클럭이 존재하고, 클럭 엣지에 동기화 되어 waveform이 생성된다.

래치 vs 플립플롭

래치는 칩이 나오는 과정에서 글리치현상을 일으켜 timing을 예측하기 어렵게 만듦.

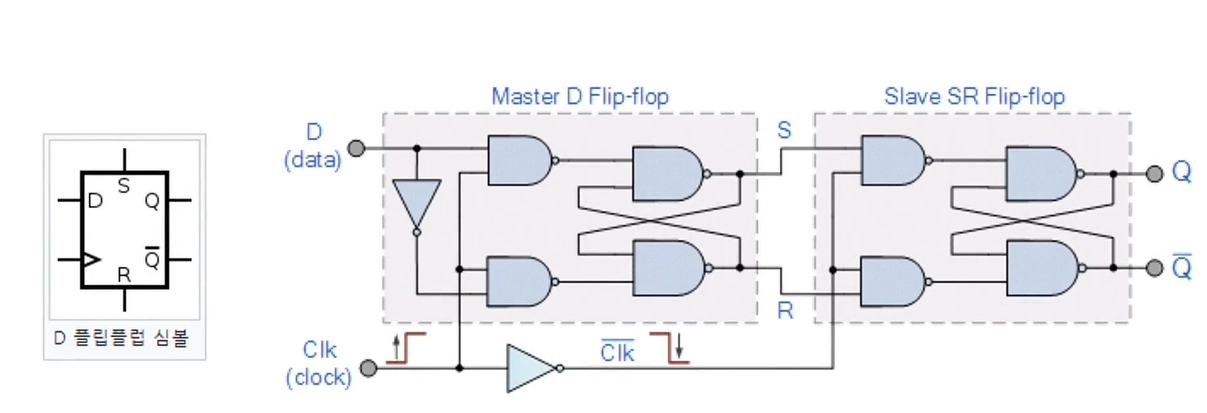

D 플립플롭

값을 저장하기 위한 로직

클럭에 동기화되어 값을 저장하고 set / reset에 의해 값을 비동기 초기화

휘발성 메모리

10개의 게이트로 구성된다.

'Verilog' 카테고리의 다른 글

| [Verilog] 주석, 수 표현 , 문자열, 식별자 (0) | 2022.12.06 |

|---|---|

| [Verilog] Verilog HDL Overview (0) | 2022.12.06 |

| [Verilog] $display (0) | 2022.11.30 |

| [Verilog] FPGA PWM (0) | 2022.10.31 |

| [Verilog] Multiplier8x8 (Mearly machine) (0) | 2022.10.28 |