Kim Seon Deok

[Verilog] Gate level modeling 본문

- gate level modeling

- concurrent assignment

- behavioral modeling

- structural modeling

gate level modeling과 concurrent assignment는 조합회로를 구현하는 데 사용된다.

behavioral moeling과 structural modeling은 조합회로와 순차회로를 구현하는 데 사용된다.

predefined primitives

베릴로그에서 기본적으로 제공되는 gate primitive이다.

정의나 선언 없이 사용가능하고 모듈 내에서만 사용할 수 있다.

initial과 always 구문 안에서는 사용할 수 없다.

userdefiined primitives

사용자가 별개로 정의하는 gate primitive를 말한다.

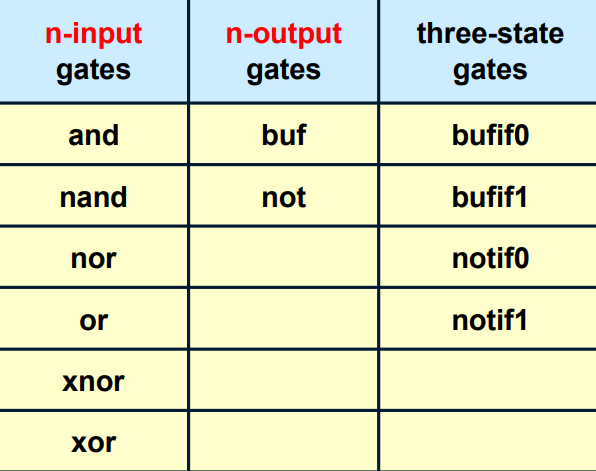

gate primitives

베릴로그에서 제공하는 gate는 다음과 같다.

| 게이트 이름 [#(n1,n2)] [인스턴스 이름] (output, input1, input2,...) |

#(n1,n2) : gate primitive 지연을 의미한다. default 지연값은 0이다. 생략 가능하다.

n1은 상승지연 n2는 하강지연이다.

인스턴스 이름은 생략 가능하지만 structural modeiling에서 하위 모듈을 인스턴스 할 땐 생략할 수 없다.

포트연결은 출력포트가 가장 먼저 오며 그 다음에 입력포트를 나열한다.

behavioral modeling구문 중 initial, always 구문 내부에서는 gate primitive를 사용할 수 없다.

and U1(out1, a. b); // 입력이 2개인 and 게이트

nor #2 U4(out4, a,b) ; // 입력이 2개인 nor 게이트. 시뮬레이션 시 지연 2

xor #(3,4) U5(out5, c,b,a) ; // 입력 3 개인 xor게이트. 시뮬레이션 시 상승 지연3, 하강지연 4

gate primitive를 이용해 1비트 full adder 구현

module full_adder(a,b,cin, sum, cout);

input a, b, cin ;

output sum, cout ;

wire s1,c1,c2 ;

xor G1(s1,a,b) ;

and G2(c1,a,b) ;

and G3(c2, s1, cin) ;

xor G4(sum, s1, cin) ;

xor G5(cout, c1, c2) ;

endmodule

buf & not gate primitive

buf b1 (out1,out2,in);

not #5 inv(out, in); // 출력값이 5ns지나면 상승, 5ns 지나면 하강. 합성 시 지연 무시됨

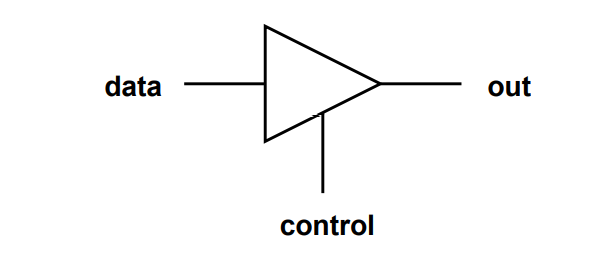

3 state buffer primitive

- 순서에 의한 매핑을 사용

1.출력포트

2.데이터 입력 포트

3.제어 입력 포트

순으로 매핑

- 3개의 지연값 지정 #(n1,n2,n3)

n1 : 상승지연, n2 : 하강지연, n3 : z로 변할 때의 지연

buf bf(out, data, control);

buf #(10,12,11) bf(out, data, control);

게이트 인스턴스의 배열

동일한 논리게이트를 여러 개 인스턴스 할 때 line 수가 길어지므로 한 문장으로 나타내도록 함

nand #2 t_nand[0:3](....) ;

nand #2 x_nand[0:7](....), y_nand[8:15](......) ;

게이트 지연과 net 지연

- 게이트 지연

게이트 입력에서부터 출력 까지 신호전달 지연

상승지연, 하강지연, turn-off지연

default 값은 0

- net 지연

net을 구동하는 driver 값이 변하는 시점부터 net값이 갱신되는 시점까지 소요되는 시간

상승지연, 하강지연, turn-off지연

default 값은 0

- 관성 지연

지정된 지연값보다 입력신호의 변화 폭이 작은 경우 입력신호가 출력에 영향 미치지 않는다.

module inerital_delay_gate() ;

reg a, b ;

and # 30(out, a, b);

initial begin

a = 1'b0

b = 1'b0 ;

#50 a = 1'b1 ; // 50ns기다리고 a,b 변경

b = 1'b1 ;

#50 a = 1'b0 ; // 50ns기다리고 a,b 변경

b = 1'b0 ;

#50 a = 1'b1 ; // 50ns기다리고 a,b 변경

b = 1'b1 ;

#20 b = 1'b0 ; // 20ns기다리고 b 변경. 관성지연 30보다 작으므로 시뮬레이션에서 무시됨

#50 ;

end

endmodule'Verilog' 카테고리의 다른 글

| [Verilog] Procedural assignment (2) | 2022.12.08 |

|---|---|

| [Verilog] Concurrent assignment (0) | 2022.12.08 |

| [Verilog] Operator (0) | 2022.12.08 |

| [Verilog] Logic status, Data type (0) | 2022.12.08 |

| [Verilog] 주석, 수 표현 , 문자열, 식별자 (0) | 2022.12.06 |