Kim Seon Deok

[컴퓨터 구조] 4-1. Single - Cycle Processor 본문

RISC-V single cycle processor 구현

"computer organization and design risc-v"를 참고하여 system call을 제외한 RISC-V 32 bit 모든 유형의 ISA에 대해 구현해 보았습니다.

case1) System verilog로 구현 후 Verilator를 사용해 synthesize

https://github.com/du6293/single_cycle_processor_systemverilog

GitHub - du6293/single_cycle_processor_systemverilog: RISC-V single-cycle-processor with system verilog

RISC-V single-cycle-processor with system verilog. Contribute to du6293/single_cycle_processor_systemverilog development by creating an account on GitHub.

github.com

case2) C언어로 구현 후 gcc환경에서 결과 확인

https://github.com/du6293/single_cycle_processor_systemverilog/blob/main/README.md

GitHub - du6293/single_cycle_processor_c: RISC-V single-cycle-processor with C

RISC-V single-cycle-processor with C. Contribute to du6293/single_cycle_processor_c development by creating an account on GitHub.

github.com

CPU 성능을 결정하는 요소

Instruction count >> ISA와 컴파일러에 의해 결정된다.

CPI 와 Cycle time >> CPU 하드웨어에 의해 결정된다.

Instruction Execution

MIPS는 폰노이만 아키텍쳐 방식을 따르기 때문에 프로그램은 항상 메모리에 있어야 한다.

프로그램을 실행하려면 프로그램은 항상 메모리 주소번지를 가지고 있는 D램에 올라와 있어야 한다.

프로그램 수행 시 PC를 사용해 포인터가 명령을 수행할 위치를 가지고 있어야 한다.

- PC -> instruction memoory, fetch instruction

- Register numbers -> register file, read registers - 레지스터 번호를 붙여 액세스

- ARM : 레지스터 32개 4비트

- MIPS : 레지스터 32개 5비트

- depending on instruction class

- Arithmetic result >> ADD, SUB 종류에 따라 ALU 이용해 계산

- Memory address for load / store >> 레지스터값과 뒤에 있는 immediator 값을 더해서 액세스 할 메모리 주소 계산

- Branch target address >> 두 레지스터 값을 비교해서 같다면 현재 프로그램 카운터 값과 immediate값을 더해 몇 개의 명령어를 뛰어야 할 지 계산

- Access data memory for load / store

- 프로그램용 메모리

- 데이터용 메모리

- PC <- target address or PC + 4 - 수행이 끝나면 프로그램 카운트 값 4 증가

위의 과정을 state machine을 이용해 순서에 따라 제어한다.

하나의 비트는 전선하나(1바이트 전선 8개, 1word 전선 32개)로, 레지스터는 플립플롭의 더미로, ALU는 조합회로를 통해 구현한다.

control을 하기 위한 state machine은 조합회로 + F/F로 구현한다.

Combinational Elements

논리회로 기본요소로 AND 게이트, Adder, Multiplexer, ALU가 있다.

특히 MUX는 여러 입력 중 selective bit을 사용해 하나의 결과값을 선택적으로 출력하도록 한다.

ALU는 다양한 연산들을 하나의 덩어리로 모아놓은 조합회로이다.

32비트 두 값을 입력으로 해서 연산한 후 하나의 32비트값을 출력으로 내보낸다.

AND,ADD,OR등 여러 연산을 하게 되는데, 이 중 MUX를 사용하 하나의 결과값만 선택한다.

Sequential Elements

레지스터는 데이터를 저장하고(플립플롭은 1비트 저장) 저장된 데이터를 업데이트 하기위해 클럭신호를 사용한다.(edge triggered). 조합회로는 클럭사이클 동안 데이터를 이동시키므로 명령어 하나가 1클럭동안 수행될 때 PC값이 증가되면서 한 단계씩 상태가 바뀌게 된다.

Instruction Formats

Single Cycle : 1클럭에 1 instruction 수행

- Add, Sub, And, Or

- Load, Store

- Branch

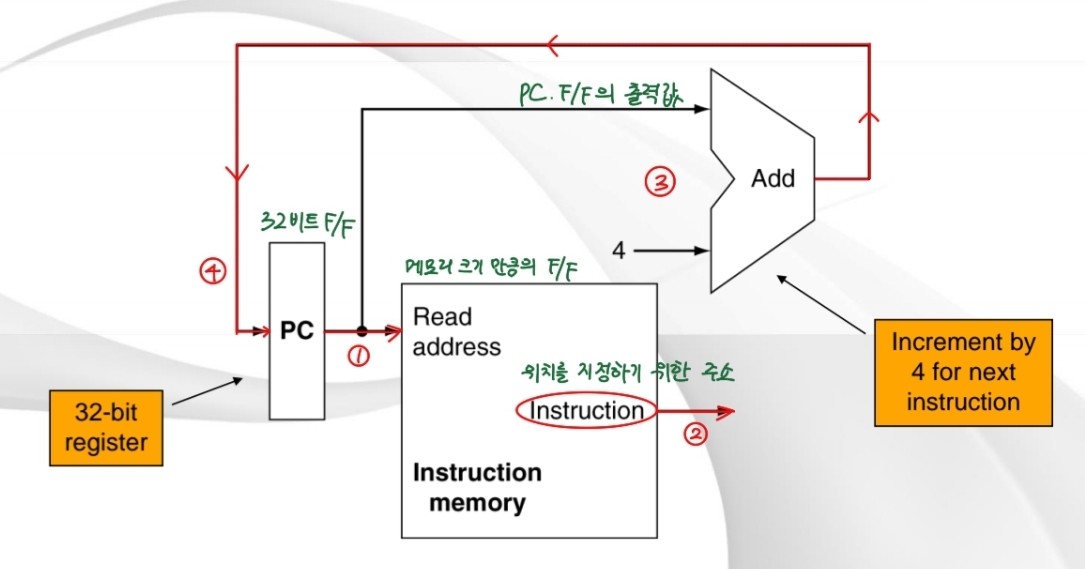

Instruction Fetch

프로그램 카운터는 실행할 명령어의 주소위치를 가리킨다. beq를 제외하고 4씩 증가한다.

- -프로그램 카운터에 저장되어 있는 메모리 주소번지에 있는 4byte를 instruction register로 가져온다. 그러면 매 클럭마다 instruction memory가 4바이트씩 끄집어져 나오게 된다. >>> 1개의 명령어가 instruction memory에서 출력됨

- 프로그램 카운터값은 또한 adder로 가서 4씩 더해져 다시 피드백 회로를 통해 프로그램 카운터의 새로운 입력이 된다.(PC+4). 다음 클럭이 들어오면 프로그램 카운터의 입력으로 새롭게 들어가게 된다.

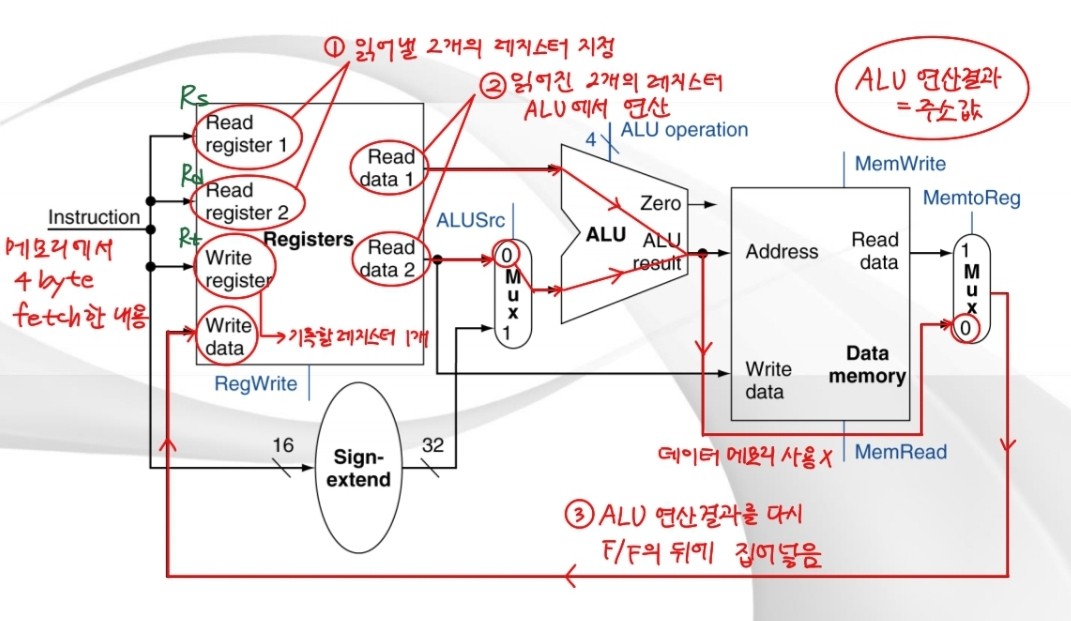

R-Format Instructions

1. 읽어낼 2개의 레지스터 지정 (read1레지스터, read2레지스터)

2. 읽어진 2개의 레지스터 ALU에서 연산. 이때 ALU연산 결과 주소값

3. ALU연산결과를 다시 F/F의 write data로 보냄

Load Instructions

1. Read1레지스터로 값 읽어옴

2. immediate 16비트값 32비트로 확장

3. 1와 2값을 ALU연산. 이 때 ALU연산 결과는 load할 주소값이다.

4. 메모리로 돌아가 3의 load할 주소값을 rt에 write(data).

Store Instructions

1.Read1레지스터로 값 읽어옴

2.immediate 16비트값 32비트로 확장

3. 1와 2 를 ALU연산. 이 때 ALU 연산 결과는 store할 주소이다.

4. Read2레지스터로 값 읽어와서 Data memory에 데이터를 write.

Branch Instructions

1. Read1레지스터, Read2레지스터로 값 읽어옴

2. 읽어온 두개의 값 ALU에서 뺄셈해서 결과값이 0인지 0이 아닌지 판단

3. 2의 결과값이 0이면 (PC + 4 + immediate해주기 위해 ) immediate 값을 16비트에서 32비트로 확장. 4번으로감.

2의 결과값이 0이아니면 PC + 4 (4의 과정x)

4. shit left 2번해서 바이트 단위 주소로 만듦

5.현재 PC값에 4의 시프트된 값을 더함. 이 때 결과값은 뛰어야 할 타겟주소인 Branch target address

Full datapath with control

R-format, Load, Store, Branch instruction, PC전체가 합쳐지고 Control 유닛이 추가된 모습이다.

그렇다 보니 2개 이상의 경로가 합쳐지므로 하나의 경로를 선택해주어야 하는 상황이 생긴다. 이 때 mux를 이용한다.

1. ALU앞 mux

- 0 : R-format레지스터값

- 1 : immediate 레지스터값

2.ALU뒤 mux

- 0 : R-format의 결과값 write

- 1 : load instruction의 결과값 write

3.Adder 뒤 mux

- 0 : PC + 4

- 1 : PC + 4 + immediate

Datapath에 추가된 Control유닛은 조합회로 덩어리로 operation 6비트를 결정한다. 따라서 single cycle machine을 완성하게 되고 1클럭 동안 1명령어를 수행하게 된다. 다음 클럭이 들어오면 control 바뀐다.

Adder 아래에 있는 and 게이트는 control 명령어가 Branch이고 reg1,reg2의 결과가 0이 아니면 각 리터럴이 1, 1이 되어 PC + 4 + immediate가 된다.

Implementing Jumps

| 2 | address |

| 6비트(31:26) | 26비트(25:0) |

26비트를 shift left하면 28비트가 되는데, 전체 32비트 중 4비트가 모자라게 되므로 PC의 상위 4비트를 잘라 붙인다.

1. control unit에서 jump명령어 선택 >> 절대점프

1. instruction[25:0]을 shift left 2번 하여 28비트로 만듦

2. PC에서4비트 잘라와 28비트인 jump address에 붙여32비트 완성

이 때 adder 뒤 mux

1 : 절대점프

0 : 절대점프를 제외한 모든 경우

Performance Issues

single cycle은 1클럭에 1개의 instruction을 수행하기 때문에 1클럭 안에 여러 format이 연산된다. 그러므로 어느 한 format이 오래 걸리게 되면 전체적인 클럭 주기가 길어지게 된다.

critical path : 가장 오래걸리는 instruction

가장 자주 사용되는 것을 빠르게 해야하는데, common case가 아닌 critical path에 초점을 맞추게 되면 성능이 오히려 나빠지게 된다. 따라서 multiple cycle로 변화하게 된다.

multiple cycle : 1클럭 1instruction 수행이 아닌 클럭주기를 줄여 여러 클럭에 걸쳐 1instruction을 수행

클럭단위별로 해야하는 일에 따라 제어워드를 만들게 된다.

성능개선의 핵심 : 오래 걸리는 instruction은 multiple cycle을 사용, 빨리 걸리는 instruction은 single cycle을 사용

'컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 4-3. Pipeline Processor (0) | 2022.11.13 |

|---|---|

| [컴퓨터 구조] 4-2. Multiple - Cycle Processor (0) | 2022.11.12 |

| [컴퓨터 구조] 2-2. MIPS (0) | 2022.11.11 |

| [컴퓨터 구조] 2-1. ARM (0) | 2022.11.10 |

| [컴퓨터 구조] 1. Abstraction and Computer tech (0) | 2022.11.04 |