Kim Seon Deok

[논리회로] 6. 레지스터와 카운터 본문

6.1 레지스터

순차회로는 플립플롭과 조합회로로 이루어져 있지만 수행하는 기능에 의해서 레지스터와 카운터로 분류한다.

레지스터 :플립플롭 여러 개의 그룹. n비트 레지스터는 n개의 플립플롭으로 이루어져있다. 각 플립플롭은 클럭을 공유하고 한 비트의 정보를 저장할 수 있다.

카운터 : 클럭(=입력펄스)가 가해짐에 따라 상태를 미리 정해진 순서대로 진행시키는 레지스터이다.

저장기능 보다는 상태천이 용도로 이용되는 특수한 형태의 레지스터이다.

위 그림은 레지스터 4개로 구성된 4비트 레지스터의 모습이다.

클럭에 not이 없으므로 상승엣지에서 동작한다. clear(=reset)신호가 뛰고 클럭이 뛰면 입력값 입력단 I0~I3에서 출력단 A0~A3으로 한번에 모든 값이 전달된다.

동기식 순차회로는 클럭 제너레이터를 가지고 있다. 발생된 펄스는 시스템의 모든 플립플롭과 레지스터에 동시에 인가된다. 위 4비트 레지스터회로는 병렬로드를 가지고 있다. 병렬로드방식은 클럭 한번으로 모든 레지스터에 값을 한번에 저장하는 방식이다. 매 클럭펄스마다 레지스터의 어떤 연산이 수행되어야 하는 지 결정하기 위한 별도의 제어신호가 사용되어야 한다.

로딩(loading) = 업데이트(updating) : 레지스터에서 새로운 정보를 전송하는 것

여기서 레지스터값을 저장하려면 1. 클럭을 안주거나 2. 클럭을 계속 주고 같은 입력을 계속 넣어주면 된다.

1.번방식은 실제로 클럭을 끊고 다시 연결하는 것을 반복하기 때문에 좋은 방법은 아니다.

2번방식을 Feedback회로를 추가한 모습은 바로 다음과 같다.

위 그림은 4비트 병렬 레지스터에 로드입력과 입력 유지회로가 추가된 모습이다.

클럭을 계속 넣어주는 상황에서,

로드 = 1 일 때 , AND 게이트 A는 작동하지 않고 AND 게이트 B가 작동한다. >> 입력단 I0~I3에서 출력단 A0~A3으로 값 전달

로드 = 0 일 때 , AND 게이트 A가 작동하고 AND 게이트 B는 작동하지 않는다. >> 출력단 A0~A3에서 스위치 A로 Feedback회로를 통해 출력값 다시 전달

즉 로드명령에 따라 AND게이트 A,B가 번갈아 작동하는 스위치 역할을 하게 된다

6.2 시프트 레지스터 (shift register, SR)

시프트 레지스터는 직렬 로드 레지스터이다.

6.1의 병렬 로드 레지스터는 한 클럭만으로 모든 레지스터에 한꺼번에 입력값을 로딩하였고,

직렬 로드 레지스터는 한 클럭에 한 비트씩 입력값을 로딩한다. >> 가지고 있는 2진 정보를 인접한 셀에 원하는 방향으로 자리옮김(shifting)하는 레지스터이다.

위 그림은 4비트 직렬 로드 레지스터의 형태이다. 한 플립플롭의 출력이 다음 플립플롭의 입력에 종속(=cascade, serial)으로 연결된 형태이다. 따라서 왼쪽에서 오른쪽 방향으로만 동작한다.

1클럭이 들어오면 4비트 숫자 중 1비트가 D 플립플롭을 타고 다음 D 플립플롭으로 넘어간다.

병렬 전송 : 모든 비트가 단일 클럭 펄스에서 동시에 로드됨

직렬 전송 : 송신 측 레지스터에서부터 나온 비트들이 수신 측 레지스터로 시프트되어 한 번에 한 비트씩 전송

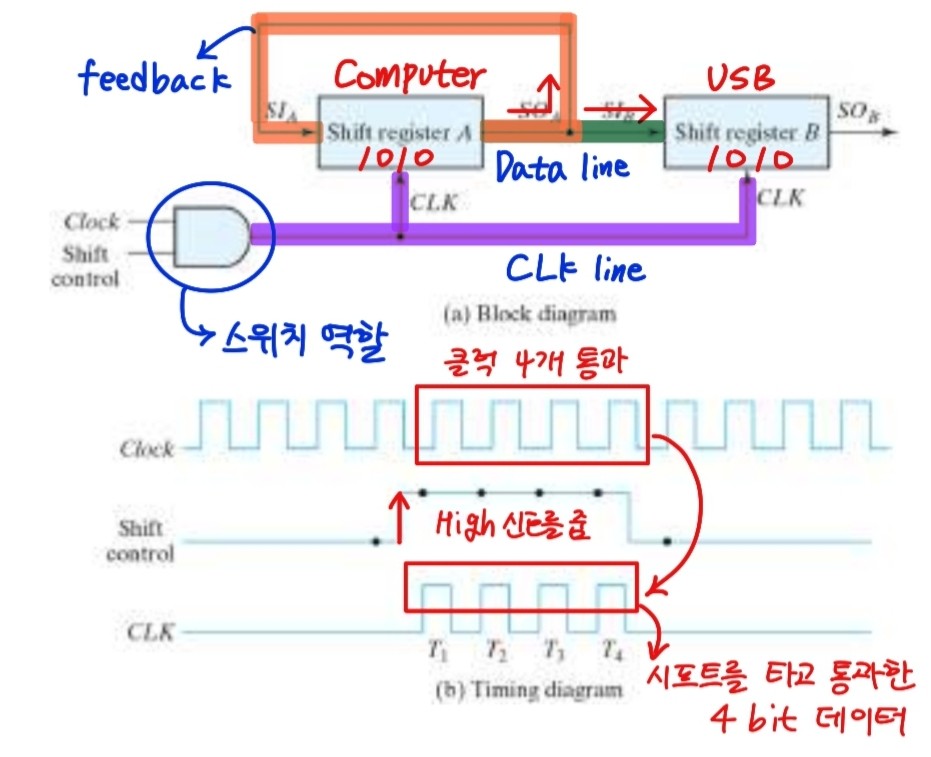

USB는 직렬전송방식을 사용한다. USB에는 4핀이 달려있는데, 각각 GND(0V), VCC(전원공급,5V), D+(data in), D-(data out)의 역할을 한다.

컴퓨터는 64bit 병렬전송방식을 사용한다. 따라서 플립플롭 64개와 64개의 선이 필요하다.

병렬로드전송을 하는 컴퓨터에 feedback회로가 연결되어 직렬전송을 한다.

컴퓨터에서 USB로 1010을 직렬전송방식을 통해 전송하는 상황을 예로 들어보면

clock이 계속 들어오는 상황에서, 시프트 컨트롤(high신호)이 들어오면 시프트를 타고 4비트 데이터가 이동하며 컴퓨터에서 USB로 data line을 지나 값이 전달된다.

만약 컴퓨터에 feedback회로가 없다면 1010이 전송되고 난 후 컴퓨터는 0000상태가 된다. 즉 컴퓨터에 파일이 지워지고 USB로 파일이 옮겨가게 됨

따라서 feedback회로를 연결해주어 컴퓨터에 카피본을 남겨두어 정보의 손실을 막는고 데이터는 순환한다.

또한 더 고속으로 데이터를 전송하려면 clock의 주기를 짧게 해주면 된다.

직렬가산

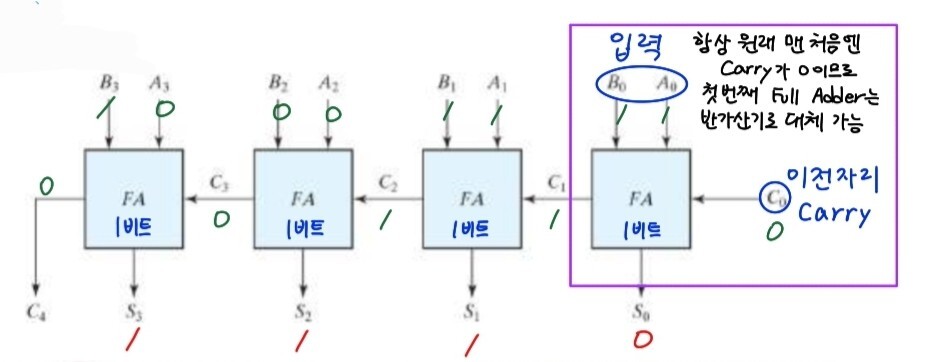

병렬방식은 직렬방식보다 속도가 훨씬 빠르다. 직렬동작은 여러 클럭주기가 필요하기 때문에 느리지만, 적은 수의 부품으로 간단한 구성이 가능하다.

위의 그림은 4비트 직렬가산기이다. 시프트 레지스터 A는 앞의 수, 시프트 레지스터 B는 뒤의 수를 저장하고, 최하위 비트쌍들의 덧셈을 시작으로 1클럭에 한 쌍씩 차례로 연산을 진행한다. 한 쌍 씩 덧셈 하는 중 캐리가 발생하면 캐리는 D플립플롭으로 전송되며. 시프트레지스터 A,B는 각각오른쪽으로 한 번 시프트 함.

4비트 연산이 끝난 후 새로운 입력값이 시프트레지스터 B에 저장되어 연산이 새롭게 또 이루어지면, 이전 결과값은 feedback회로를 통해 다시 A의 입력으로 들어온다. 따라서 시프트 레지스터A에 합을 누적하면서 2번째 3번째 수가 더해질 수 있다.

4비트 기준 직렬가산기는 시프트 레지스터 2개와 전가산기 1개로 연산하여 전가산기 3개를 절약하게 되어 비용 절감의 효과를 가져다 준다. 뿐만 아니라 시프트 레지스터는 원래 컴퓨터에 있기 때문에, 실질적으로 전가산기 1개만 사용하면 된다. 또한 직렬로 연산을 하기 때문에, 한번에 연산이 끝나지 않아 계산을 4번 해주어야 하므로 시간이 오래 걸린다는 단점이 있다. 결론적으로 병렬가산이 더 효율적이라 볼 수 있다.

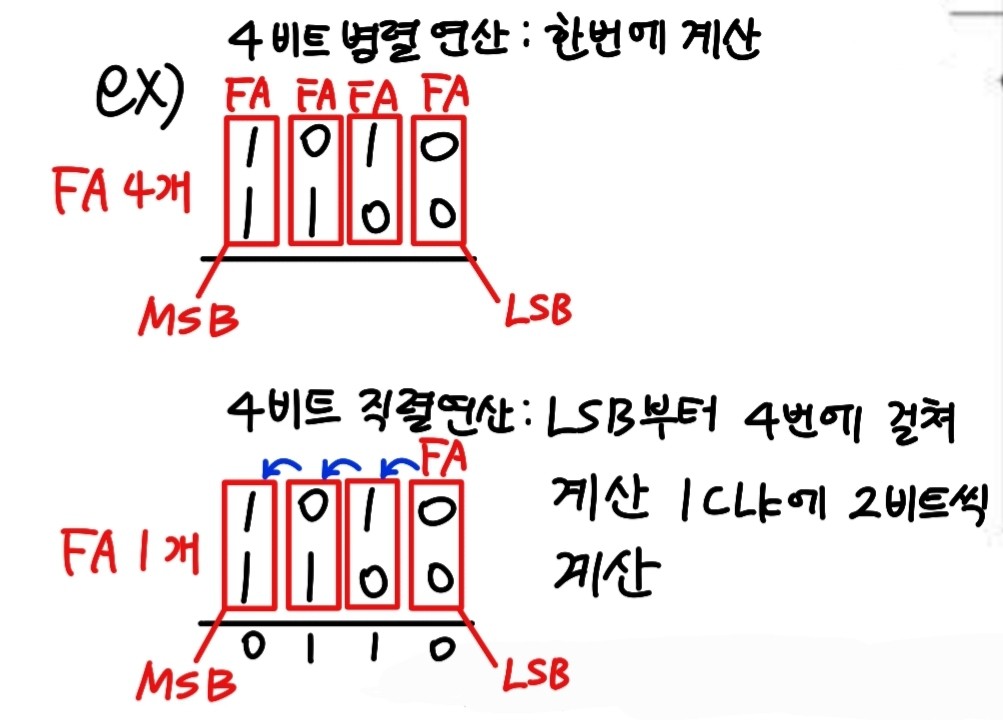

위의 그림은 4장의 4비트 병렬전가산기로, 전가산기 4개로 구성되어 있으며 병렬적으로 덧셈을 수행해 연산 속도가 빠르다.(동시에 A0+B0, A1+B1,A2+B2,A3+B3 진행)

4비트 기준

병렬 가산기 - 전가산기 4개 이용, 한꺼번에 4비트를 동시에 계산 // 병렬 로드가 있는 레지스터 사용

// 레지스터를 제외하면 조합회로이다.

직렬 가산기 - 전가산기 1개, 시프트 레지스터 2개 이용, 4번에 걸쳐 계산.(1클럭 당 2비트씩 짝을 지어 계산) // 1개의 전가산기, 1개의 캐리 플립플롭 사용 // 순차회로이다.

JK플립플롭을 사용해 직렬가산기를 구현한 것이다.

쌍방향 시프트 레지스터 (universial shift register)

그동안 시프트 레지스터는 한방향으로만 시프트하는 단방향 시프트 레지스터였다.

양방향(bidirectional) : 양쪽방향으로 시프트

쌍방향 시프트(universial) : 양쪽방향으로 시프트 + 병렬로드 기능

위의 그림은 4비트 쌍방향 레지스터이다. 상단의 가로로 길게 표시된 보라색 박스는 이전의 4비트 병렬 로드 레지스터이다. 하단은 4 to 1 mux 4개를 이어붙인 형태이다.

1. selective bit가 s1,s0 = 0,0일 때

mux의 0번 입력이 mux의 출력 y와 연결된다. D플립플롭의 feedback회로를 통해 Q로 y값이 전달된다.

전원을 주고있는 동안에는 입력값을 저장만 한다.

>> No change

2. selective bit가 s1,s0 = 0,1일 때

I3에 오른쪽 시프트를 하기 위한 입력이 들어감

mux3의 1번 입력이 mux3의 출력 y와 연결된다.

D3플립플롭의 출력 Q3는 오른쪽에 있는 MUX2의 1번단자와 연결

D2플립플롭의 출력 Q2는 오른쪽에 있는 MUX1의 1번단자와 연결

D1플립플롭의 출력 Q1는 오른쪽에 있는 MUX0의 1번단자와 연결

>> 오른쪽 시프트

3. selective bit가 s1,s0 = 1,0일 때

I0에 왼쪽 시프트를 하기 위한 입력이 들어감

mux0의 2번 입력이 mux0의 출력 y와 연결된다.

D0플립플롭의 출력 Q0는 왼쪽에 있는 MUX1의 2번단자와 연결

D1플립플롭의 출력 Q1는 왼쪽에 있는 MUX2의 2번단자와 연결

D2플립플롭의 출력 Q2는 왼쪽에 있는 MUX3의 2번단자와 연결

>> 왼쪽 시프트

4. selective bit가 s1,s0 = 1,1일 때

I0은 MUX0의 3번단자와 연결되고, A0로 출력

I1은 MUX1의 3번단자와 연결되고, A1로 출력

I2은 MUX2의 3번단자와 연결되고, A2로 출력

I3은 MUX3의 3번단자와 연결되고, A3로 출력

>> 4비트 병렬 로드 레지스터와 동일

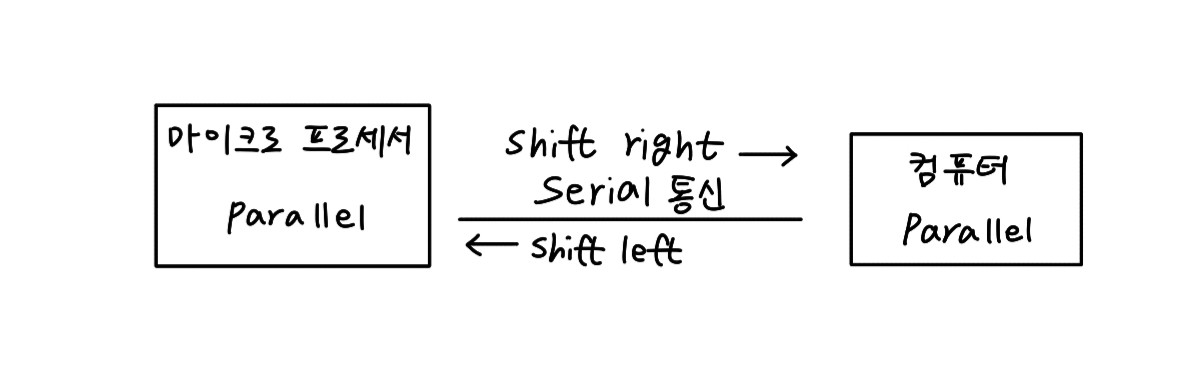

시프트 레지스터는 멀리 떨어져 있는 디지털 시스템들의 통신에 이용된다.

서로 다른 두 위치에 n비트를 전송한다 가정하면 병렬로 n개의 전선을 길게 사용하는 방법이 비경제적일 수 있다. 따라서 하나의 라인을 사용하여 직렬방식으로 한 비트씩 전송하는 것이 경제적이다.

마이크로프로세서 내부에서는 n비트 데이터를 병렬로 읽어서 하나의 전선을 통해 외부로 직렬방식으로 데이터를 전송하고 수신단에서는 시프트 레지스터를 통해 직렬방식으로 들어오는 데이터를 수신한다. n비트가 수신되면 레지스터를 병렬방식으로 출력한다.

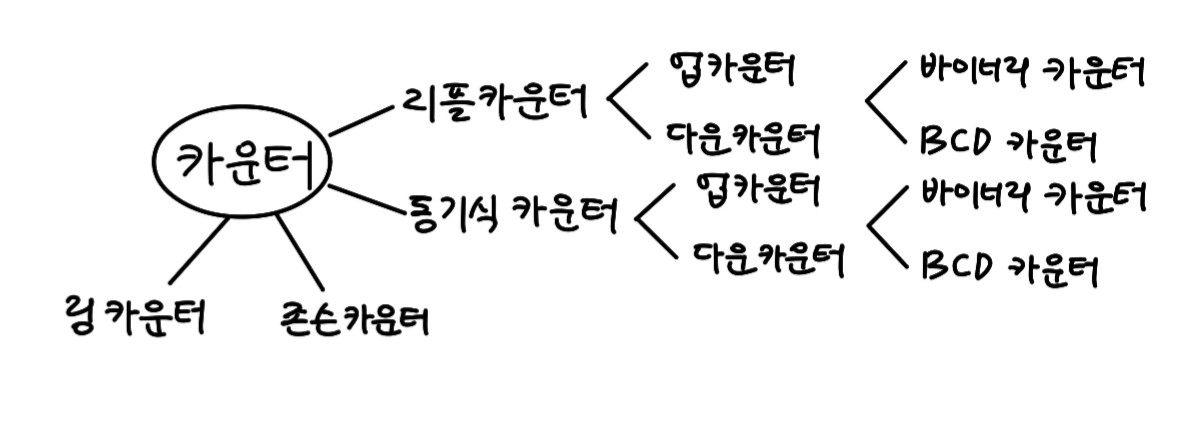

카운터의 방식 및 차이점

1. 리플 카운터 = 비동기식 카운터: 클럭이 1개만 연결(주로 LSB) 되어있어, 출력이 다음 클럭의 역할을 함, 플립플롭의 천이가 다른 플립플롭을 트리거 하는 소스로 동작한다, 주로 보수에만 사용된다.

전파지연의 단점을 가지고 있다.

2. 동기식 카운터 : 클럭이 모든 플립플롭과 연결되어있어, 플립플롭의 클럭 입력은 공통된 클럭으로부터 공급된다.

보수, 유지에 동시에 사용된다.

6.3 리플 카운터 (ripple counter) = 비동기식 카운터(asynchronous counter)

카운터는 특수한 일을 하는 레지스터이다.

카운터 : 입력 펄스에 따라 정해진 순서대로 상태가 변하는 레지스터. 어떤 사건의 발생횟수를 세거나 동작순서를 제어하는 타이밍 신호를 만들 때 이용된다. n비트 2진 카운터는 n개의 플립플롭으로 구성되며 0 ~ (2^n-1) 까지 카운트한다.

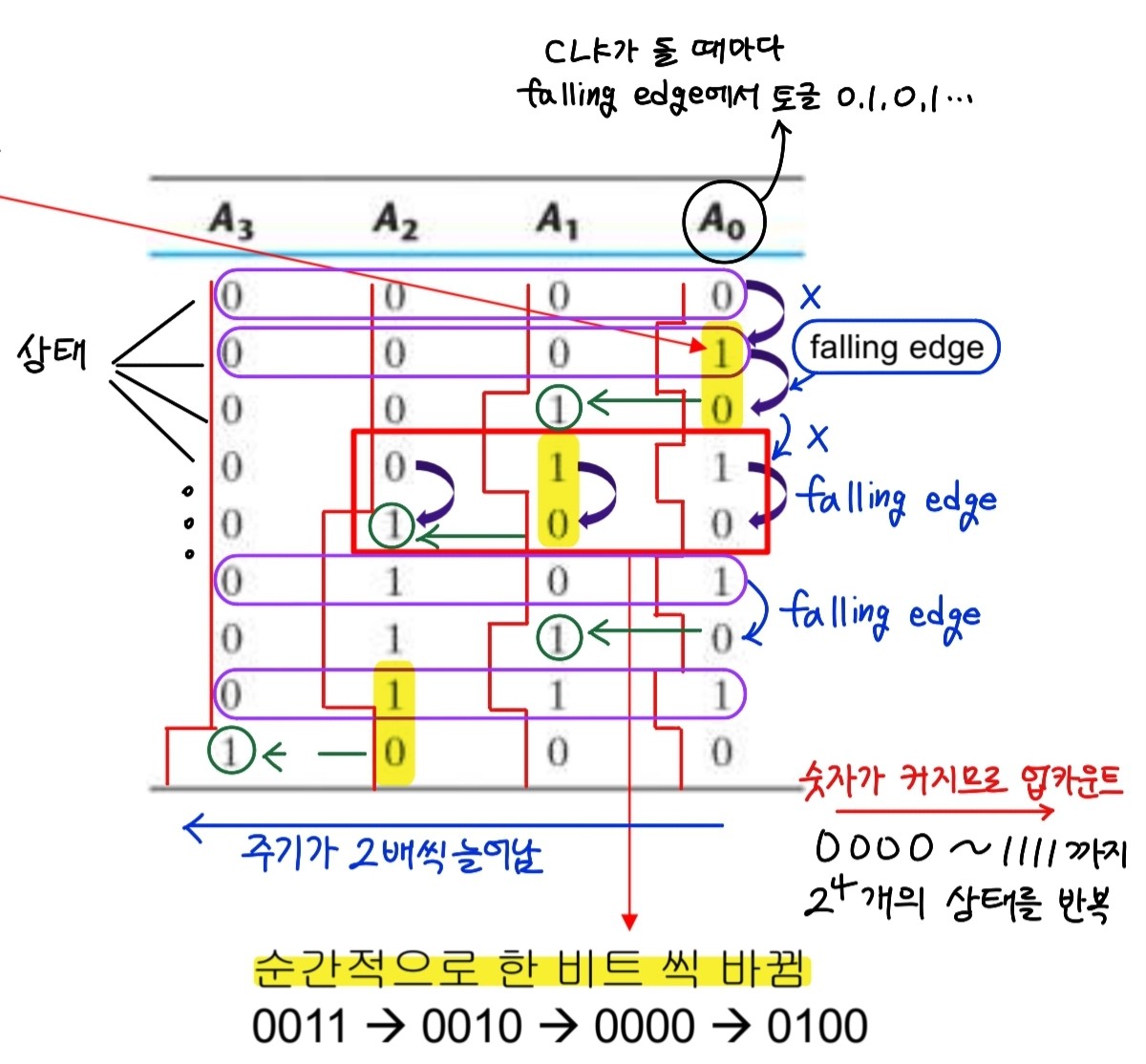

6.3.1 업카운터

위 그림은 T 플립플롭을 사용한 리플 업카운터와 D 플립플롭을 사용한 리플 업카운터이고, 모두 카운트단자에 not게이트가 연결되어 있으므로 하강엣지에서 동작한다. 이전 플립플롭의 출력이 다음 플립플롭의 클럭으로 들어간다.

0000 ~ 1111까지 2^4개의 상태를 반복하며, 숫자가 점점 증가하므로 업카운트이다.

특히 D 플립플롭을 사용한 4비트 바이너리 리플 카운터는 입력단자 D가 Q'으로 연결되는 feedback회로가 추가되어 있다.

출력 A0는 클럭이 들어올 때마다 하강엣지에서 0,1,0,1...로 토글한다.

출력 A1은 A0의 주기의 2배로 토글한다.

출력 A2는 A1의 주기의 2배로 토글한다.

출력 A3은 A2의 주기의 2배로 토글한다.

>> 주기가 2배씩 늘어난다.

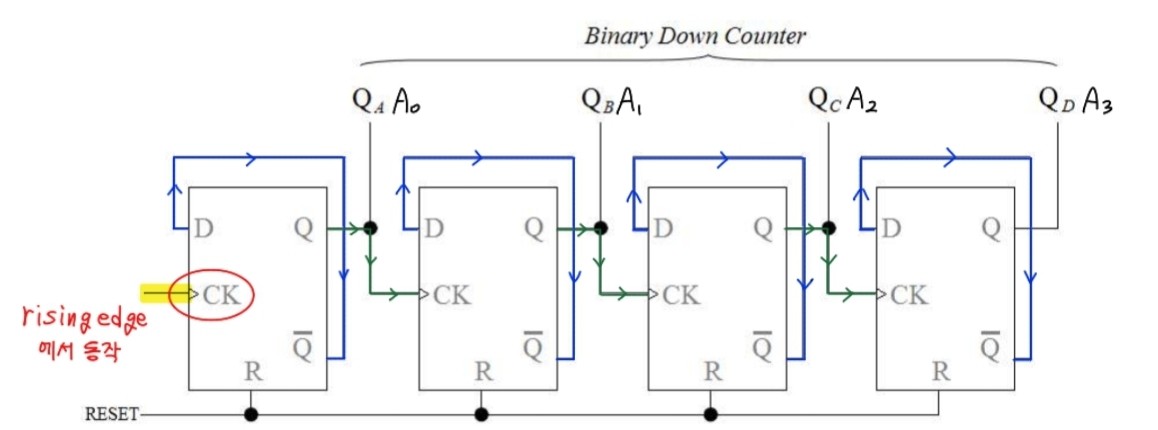

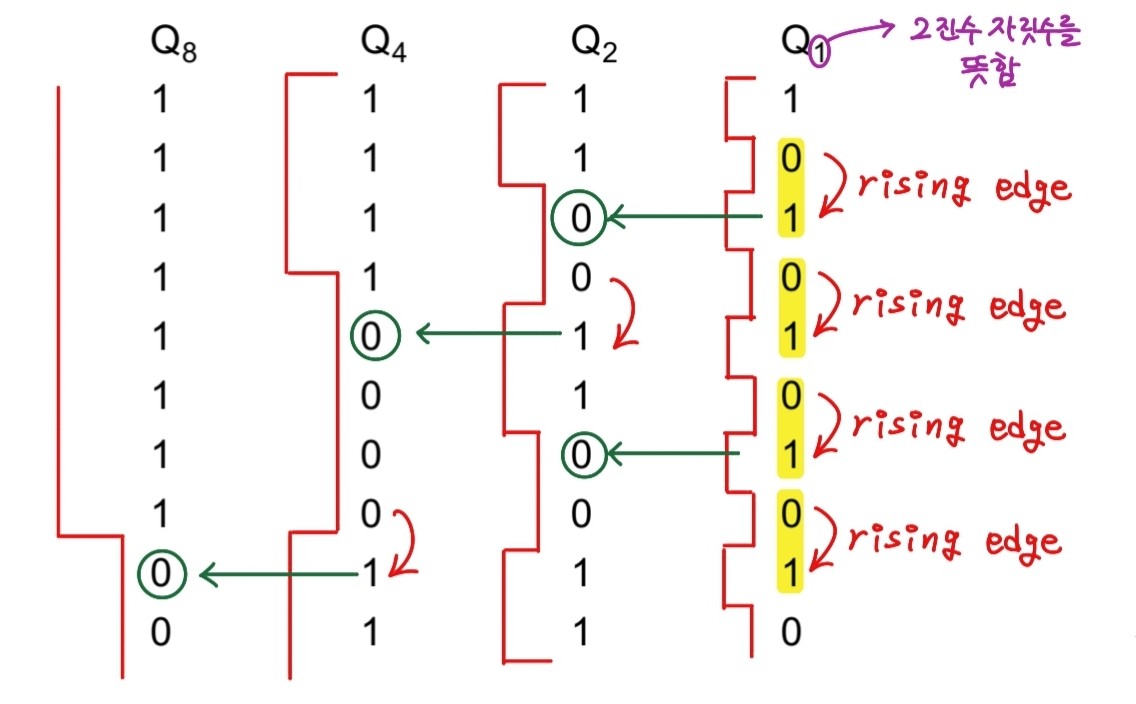

6.3.2 다운 카운터

위 그림은 D 플립플롭을 사용한 리플 다운카운터이다. 입력단자 D가 Q'으로 연결되는 feedback회로가 추가되어 있다.

카운트단자에 not게이트가 없으므로 상승엣지에서 동작한다. 이전 플립플롭의 출력이 다음 플립플롭의 클럭으로 들어간다. 1111 ~ 0000까지 2^4개의 상태를 반복하며, 숫자가 점점 감소하므로 다운카운트이다.

출력 A0는 클럭이 들어올 때마다 상승엣지에서 1,0,1,0...로 토글한다.

출력 A1은 A0의 주기의 2배로 토글한다.

출력 A2는 A1의 주기의 2배로 토글한다.

출력 A3은 A2의 주기의 2배로 토글한다.

>> 주기가 2배씩 늘어난다.

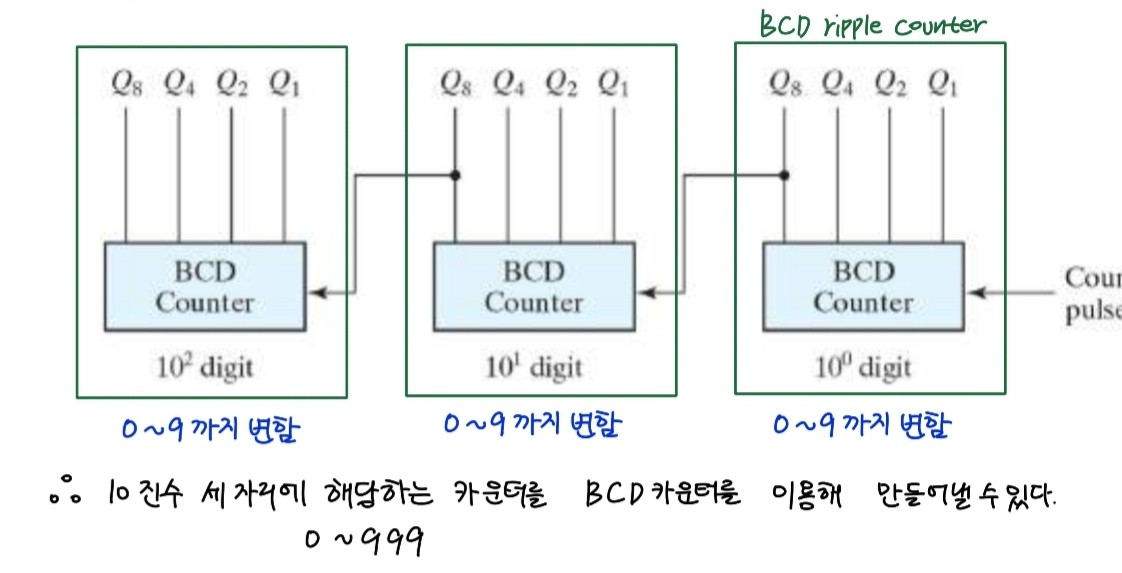

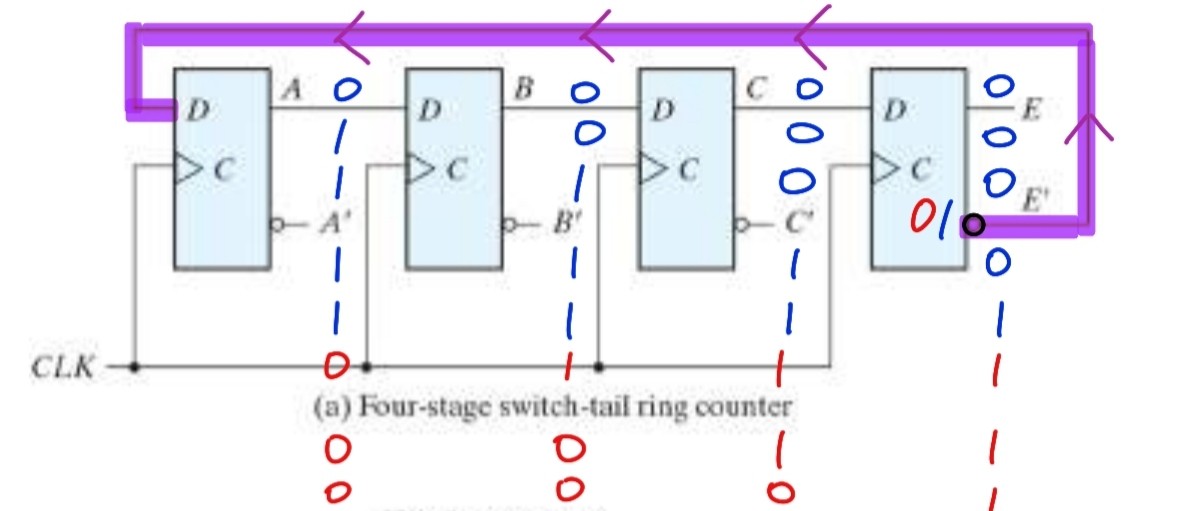

6.3.3 BCD 리플 카운터

4비트를 사용하므로 4개의 플립플롭이 필요하고, decimal이므로 10개의 상태를 나타낸다.

1001이 나오면 reset해 0000으로 만들어, 0000 ~ 1001까지 10개의 상태를 반복한다.

위 그림은 BCD리플카운터이다. jk플립플롭을 이용하였다. 카운트단자에 not게이트가 붙어있으므로 하강엣지에서 토글한다.

이전 플립플롭의 출력이 다음 플립플롭의 클럭으로 들어간다. 추가로 1001이 나오면 reset해 0000으로 만들어주어야 하므로, Q'8단자가 J2단자로 연결되어있고, and 게이트를 추가함

J8 = 0, K8=1이면 Q8 = 0, Q'8=1일 때 J2단자가 0이 된다.

Q2,Q4가 동시에 1일 때 Q8이 0 > 1로 토글된다.

세자릿수의 decimal BCD 카운터의 그림이다. 3개의 BCD 리플카운터로 구성되어 있다. 각 리플 카운터는 0 ~ 9까지 변하고 10진수 3자리에 해당하는 카운터를 BCD 카운터를 이용해 0 ~ 999까지 만들어낼 수 있다.

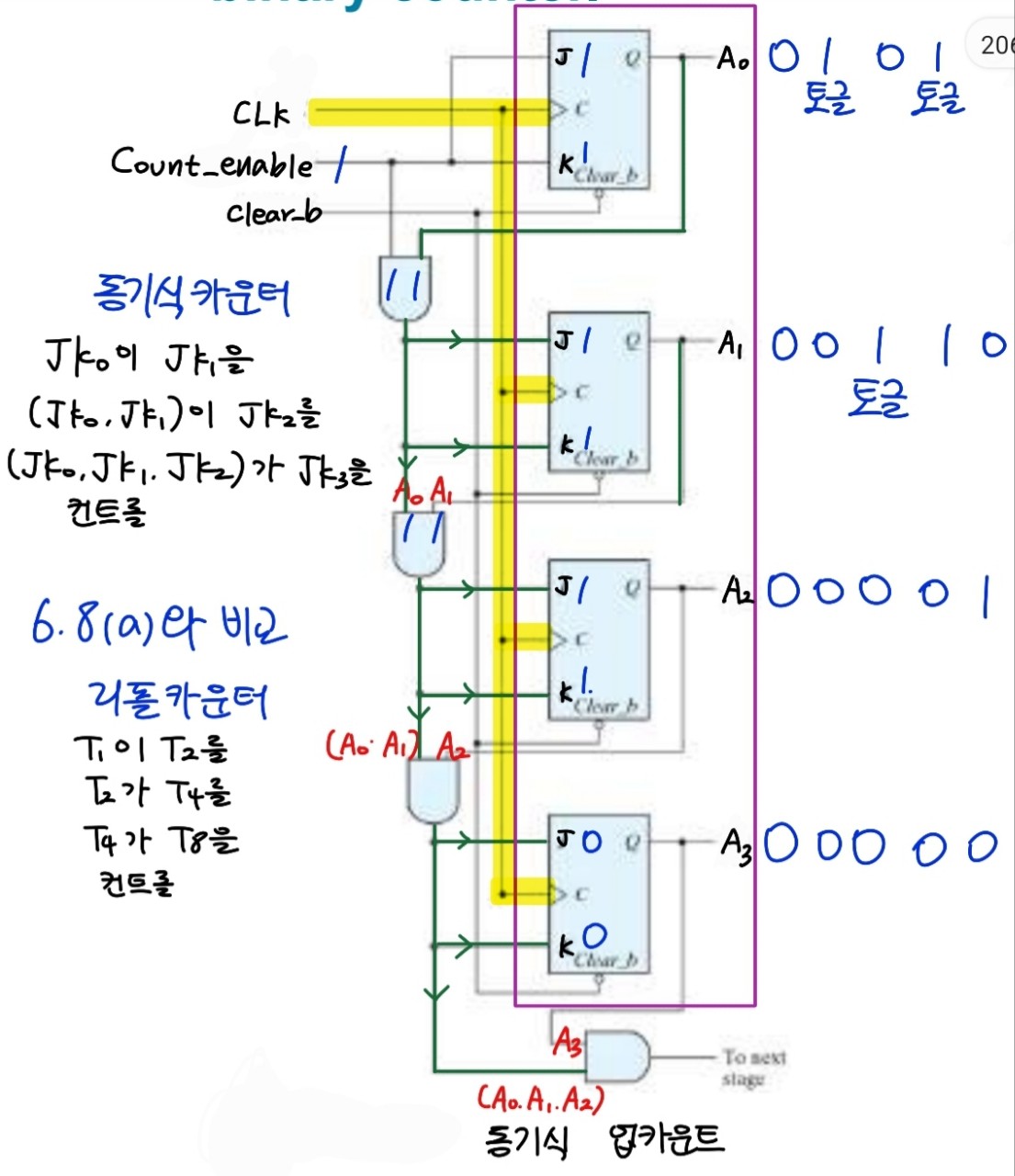

6.4 동기식 카운터 (synchronous counter)

동기식 카운터 : 모든 플립플롭이 하나의 공통클럭에 연결되어 있어서 클럭펄스가 모든 플립플롭의 입력으로 가해진다. 공통된 클럭이 모든 플립플롭을 동시에 트리거시킨다.

T플립플롭을 사용했을 때 T = 0이거나, JK 플립플롭을 사용했을 때 J = K = 0이면 변하지 않고

T플립플롭을 사용했을 때 T = 1이거나, JK 플립플롭을 사용했을 때 J = K = 1이면 플립플롭이 토글된다.

6.4.1 업카운터

위 그림은 4비트 동기식 바이너리 카운터의 모습이다. 이전 T,D 리플 업카운터와 다르게 모든 플립플롭에 클럭이 연결되어 있다.

출력 A0는 클럭이 들어올 때마다 상승엣지에서 1,0,1,0...로 토글한다.

A0이 1일 때 Enable이 가해지면 JK1플립플롭으로 전달되고 A1은 0 > 1이 된다.

A1이 1일 때 Enable이 가해지면 JK2플립플롭으로 전달되고 A2는 0 > 1이 된다.

A2이 1일 때 Enable이 가해지면 JK3플립플롭으로 전달되고 A3는 0 > 1이 된다.

이전출력이 다음 플립플롭의 클럭으로 들어가는 리플카운터와 다르게

JK0은 JK1을, (JK0,JK1)은 JK2를, (JK0,JK1,JK2)는 JK3을 컨트롤 하는 구조이다.

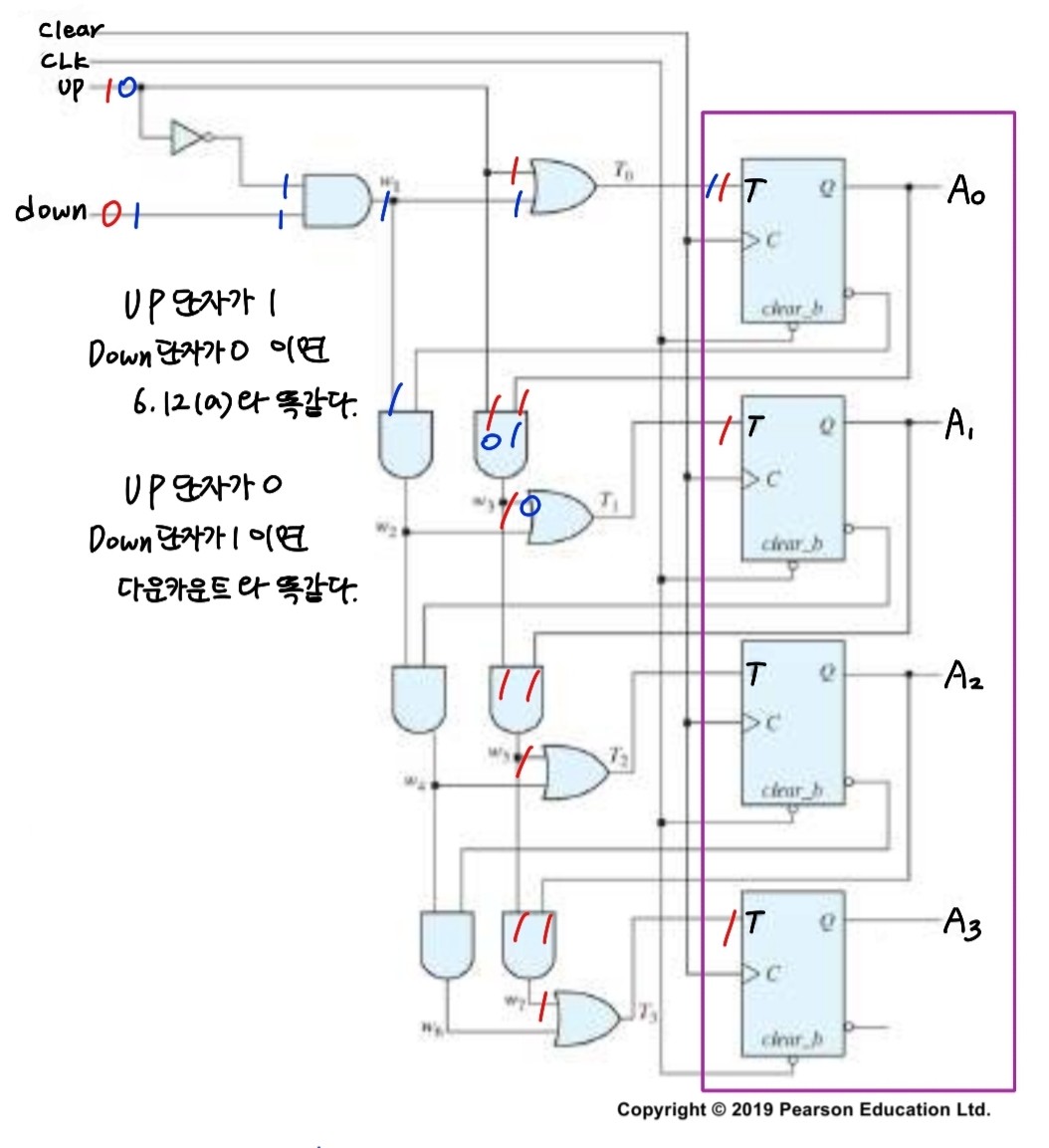

6.4.2 업다운바이너리카운터

위 그림은 4비트 업다운 바이너리 카운터의 모습이다. AND게이트는 스위치 역할을 한다.

UP단자가 1 DOWN단자가 0 이면 업카운트와 같고

UP단자가 0 DOWN단자가 1 이면 다운카운트와 같다.

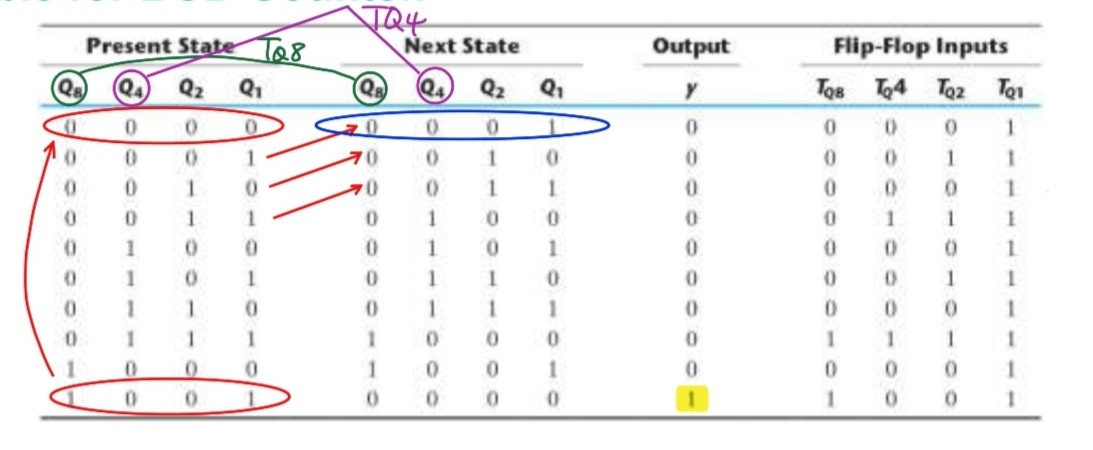

6.4.3 BCD 동기식 카운터

2진으로 코드화된 10진수를 0000~1001까지 세고 다시 0000으로 되돌아감.

위 그림은 병렬 로드를 사용한 bcd카운터이다.

두 회로 모두 0000 ~ 1001까지 카운트한 후 0000으로 다시 돌아간다.

(A)는 1001이 되기 전까지 AND게이트의 출력이 0인 동안 상승클럭이 카운트를 하나씩 증가시킨다. 1001이 되면 AND게이트 출력이 1이 되어 LOAD = 1이 되고, 그 다음 클럭에서 0000의 출력값을 내보낸다.

(B)는 1001을 지나 1010이 되는 순간 AND게이트를 통해 0000으로 CLEAR된다.

잠깐동안 1010이 되었다가 0000이 되므로 Spike가 발생한다.

바이너리 카운터의 경우 0000 ~ 1001을 지나 1010, 1011...점점 숫자가 커지지만

BCD카운터의 경우 0000 ~ 1001을 지나 0000으로 되돌아가며 carry가 발생한다.

위 상태표를 이용해 카르노맵으로 간략화 하여 특성식을 얻고, TQ8,TQ4,TQ2,TQ1의 T플립플롭 4개로 논리도를 만들 수 있다.

6.4.4 바이너리 카운터

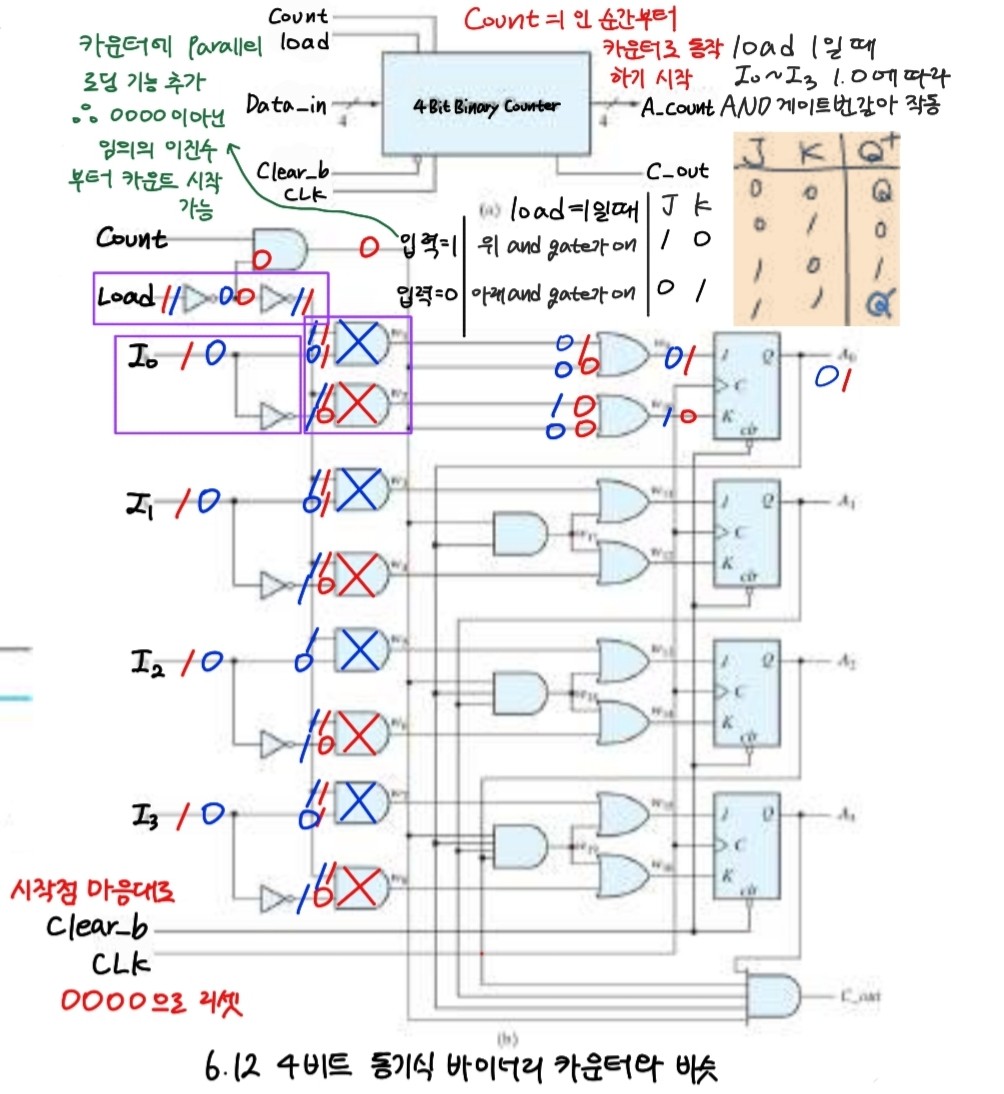

위 그림은 병렬로드를 가진 4비트 바이너리 카운터이다.

카운터에 병렬로드가 추가되어 0000부터가 아니라 임의의 이진수부터 시작하여 카운트가 가능해졌다.

카운트의 마지막 지점은 CLEAR를 이용한다.

CLEAR_B가 0으로 떨어지면 모두 0000으로 리셋된다.

LOAD = 0이고 COUNT = 0일 때 상태를 유지 한다.

LOAD = 0이고 COUNT = 1일 때 카운트 동작을 한다.

CLEAR_B = 1이고 LOAD = 1 일 때, 카운트 동작은 멈춘다.

I0 ~ I3 = 1이면, 각각의 입력단자와 연결된 AND게이트 2개 중 위의 것만 작동하고 J = 1,K = 0이 되어 출력값은 1이다.

I0 ~ I3 = 0이면, 각각의 입력단자와 연결된 AND게이트 2개 중 아래의 것 작동하고 J = 0,K = 1이 되어 출력값은 0이다.

따라서 LOAD가 1일 때 입력단자 값이 1인지 0인지에 따라 AND게이트가 번갈아 작동한다.

6.5 링카운터 & 존슨카운터

n개의 플립플롭을 가진 회로는 2^n개의 2진 상태를 가지지만, 모든 상태가 필요하지 않을 수 있다.

사용되지 않는 상태는 상태표에 나타내지 않고 don't care 조건이 되거나 특정한 다음 상태에 인가된다.

사용되지 않는 상태를 순차회로로 설계할 땐 사용되지 않는 상태의 다음 상태를 분석해주어야 한다.

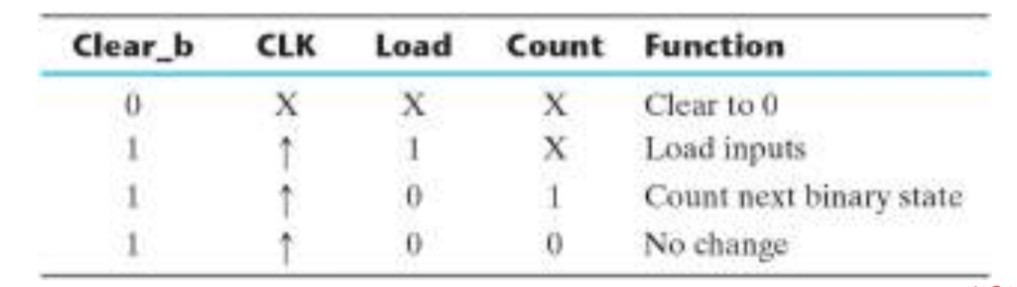

JK플립플롭 3개를 사용하면 000 ~ 111까지 상태 8개를 만들 수 있다. 이 중 상태 6개만 이용하고 나머지(000,111)는 don't care로 사용하면 다음과 같다.

상태표를 이용해 카르노맵을 만들고 특성식을 구하면 JA=B,KA=B, JB=C,KB = 1, JA=B',KC = 1

A=1,B=1,C=1인 don't care 상태로부터 출발하면 B단자와 연결된 JA = 1, KA = 1이 되어 A는 1 > 0으로 토글

C단자와 연결된 JB = 1, KB = 1이 되어 B는 1 > 0으로 토글

B'단자와 연결된 JC = 0이고 KC = 1이므로 C는 1 > 0

따라서 don't care상태의 입력을 넣어주더라도 다음 클럭이 들어가면 000으로 돌아가 don't care가 아닌 것들만 사용한다.

링 카운터

임의의 시간에 하나의 플립플롭만 세팅되고 나머지 플립플롭은 모두 클리어된 상태로 동작하는 순환식 시프트 레지스터

2 ^n개의 타이밍 신호를 발생시키기 위한 구현 방법

1. 2^n개의 플립플롭으로 구성된 시프트 레지스터 이용

2. n to 2^n라인 디코더를 이용한 n비트 레지스터 이용 >> 훨씬 경제적

1000의 4비트를 링카운터를 이용한다 하면

4비트의 숫자들을 각각 시프트 레지스터 4개를 사용해 오른쪽으로 시프트한다. 1000 > 0100 > 0010 > 0001 > 1000의 4가지 상태가 반복된다.

플립플롭을 2개로 구성된 2비트 바이너리 카운터와 디코더를 연결하면 2^2개의 출력 중 1개만 1이되며,

훨씬 적은 갯수의 플립플롭을 사용해 링카운터와 같은 결과를 얻을 수 있다.

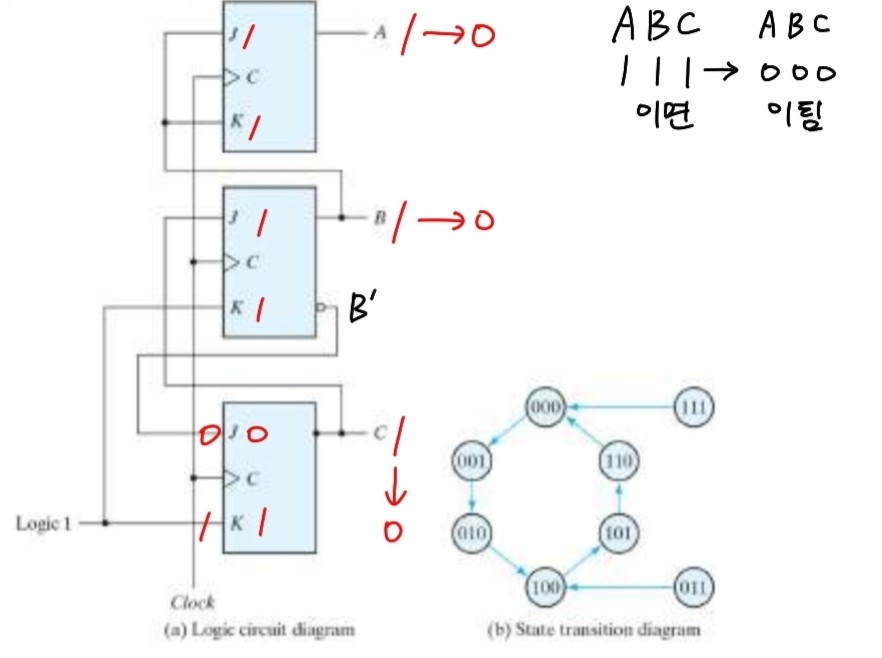

존슨 카운터

링카운터가 업그레이드 된 형태이다. n비트 링카운터는 n개의 다른 상태를 공급하기 위해 단일 비트가 플립플롭 사이를 순환한다. switch-tail링카운터로 연결하면 2n개의 상태로 동작한다.

링카운터는 플립플롭 n개로 상태 n개를 표현하지만 존슨카운터는 플립플롭 n개로 상태 2n개를 표현한다.

D플립플롭은 값을 저장하고 다음 플립플롭으로 넘겨주는 역할을 함

0000(시작) > 1000 > 1100 > 1110 > 1111 이 때 1111이 되는 순간 E'단자가 1 > 0으로 바뀌게 된다.

0111 > 0011 > 0001 > 0000

4비트 기준 0000,1111이면 알파벳의 양 끝을, 그 외에는 플립플롭의 값이 0 > 1 or 1 > 0 으로 바뀌는 경계를 알파벳으로 표현한다.

'논리회로' 카테고리의 다른 글

| [논리회로] 7. 메모리 및 프로그래머블 논리 (0) | 2022.10.24 |

|---|---|

| [논리회로] 5. 동기식 순차 논리 (0) | 2022.10.17 |

| [논리회로] 4. 조합논리 (0) | 2022.10.14 |

| [논리회로] 3. 게이트 레벨 최소화 (0) | 2022.10.12 |

| [논리회로] 2. 부울 대수와 논리 게이트 (0) | 2022.10.10 |