Kim Seon Deok

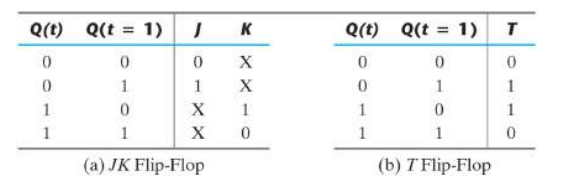

[논리회로] 5. 동기식 순차 논리 본문

5.1 순차회로

조합회로 : 출력이 입력에 의해서만 즉각적으로 결정됨. 과거의 입력에 영향을 받지 않음

순차회로 : 조합회로 + 기억장치로 구성되며, 기억장치에 저장된 값을 입력에다 다시 전달하는 feedback회로를 이룬다. 기억장치는 2진정보를 저장하며 순차회로의 상태를 저장한다.

따라서 순차회로는 현재상태와 외부입력으로부터 출력값을 결정하고, 외부 입력은 기억요소들의 상태변화에 대한 조건을 결정한다. 기억장치는 동기식 비동기식으로 구분된다.

동기화 : clock generator(클럭발생기. 타이밍 장치)에서 주기적으로 clock pulse 신호를 생성한다.

동기식(synchronous) 순차 논리회로 = 클럭형 순차회로 : 회로 내의 동작과 저장된 값의 최종적인 갱신이 클럭펄스 발생과 동기화 됨

ex) 두 2진수를 더하고 저장하는 회로는 숫자의 값으로부터 합을 계산하고 클럭 펄스 발생 시 그 합을 저장

동기식 순차 회로에 사용되는 저장요소는 플립플롭이다.

비동기식(asynchronous) 순차 논리회로

트리거(trigger) : 래치 혹은 플립플롭의 제어 입력이 변경되면 상태가 전환되는 것을 말한다.

5.2 래치(latch)

디지털 회로의 저장 요소 : 회로에 전력이 공급되는 한 (= 클럭이 들어와 있는 동안에만), 입력에 의해 상태를 바꾸도록 지시할 때까지 2진상태를 유지한다.

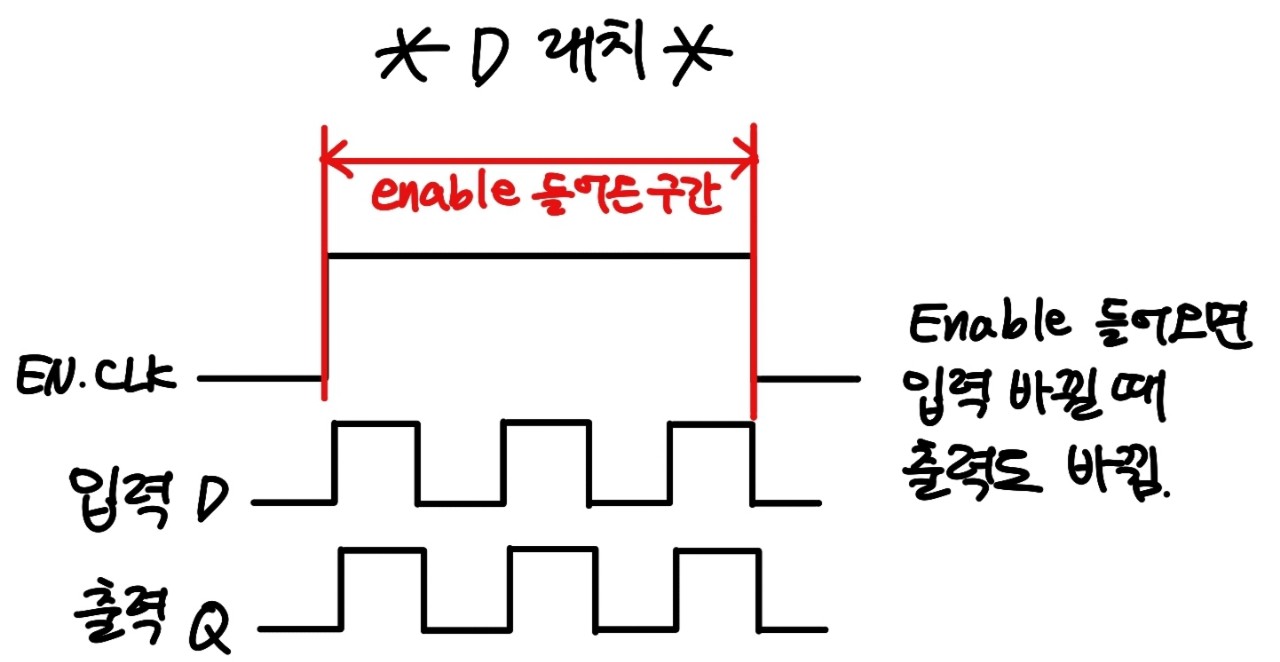

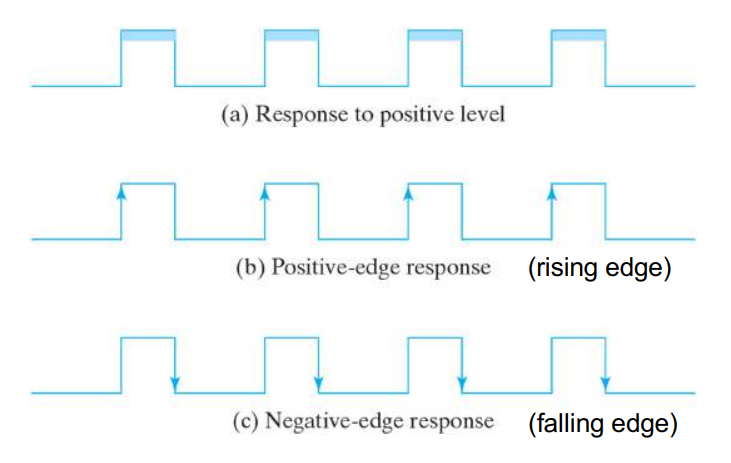

래치는 신호 레벨에 의해 동작하는 저장요소로, 레벨 반응형이다. enable을 주고 전압 레벨이 유지되는 동안에 입력이 바뀌면 구간동안 출력이 바뀐다. 래치는 플립플롭을 이루는 더 작은 element이다.

래치는 비동기 순차회로를 설계하고 2진 정보를 저장하는 데 유용하지만, 실질적으로 동기 순차회로에는 사용하지 않는다.

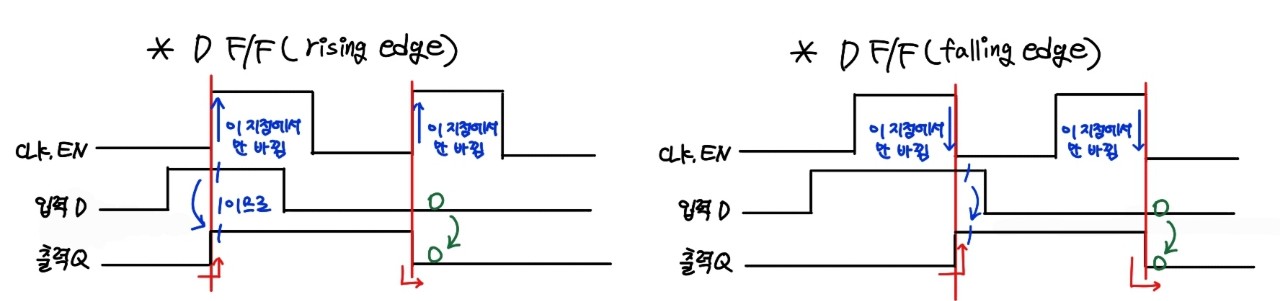

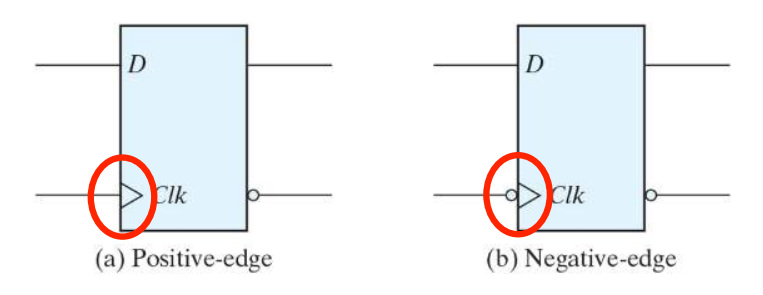

플립플롭은 클럭천이에 의해 제어되는 저장요소로, 에지반응형이다. enable을 주고 rising edge(=positive edge) 혹은 falling edge(=negative edge)일 때에만 동작한다. 이 차이점은 매우 중요하다.

플립플롭은 제일 간단한 메모리로, 2진수 숫자 개( = 1 bit)를 저장한다.

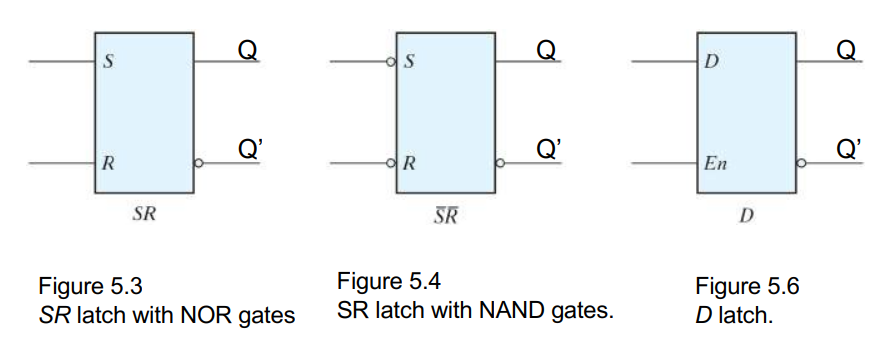

SR래치

SR래치는 cross-coupled NOR게이트 또는 NAND게이트로 구성되는 저장장치이다.

| S | R | Q | Q' |

| 0 | 0 | 상태유지 | |

| 1 | 0 | 1 (SET) | 0 |

| 0 | 1 | 0 (RESET) | 1 |

| 1 | 1 | FORBIDDEN | |

NAND게이트로 구현된 S'R'래치이다. NOR게이트를 사용했을때와 결과가 보수의 결과를 갖는다.

| S | R | Q | Q' |

| 0 | 0 | FORBIDDEN | |

| 1 | 0 | 0 (RESET) | 1 |

| 0 | 1 | 1 (SET) | 0 |

| 1 | 1 | 상태유지 | |

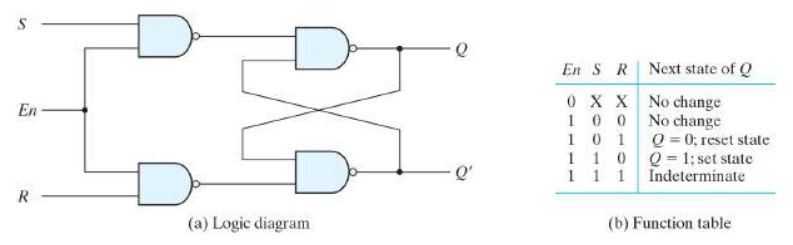

제어 입력(ENABLE)을 가진 SR래치

제어입력을 가진 SR래치는 앞선 S'R'래치에 NAND 게이트 2개와 ENABLE단자가 추가로 연결된 모습이다.

ENABLE단자가 0이면 S,R에 상관없이 상태유지만 한다.

ENABLE단자가 1이면 동작을 하게 되는데, SR게이트와 동일하게 동작한다.

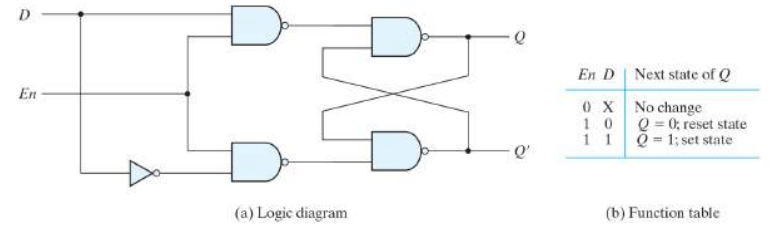

D래치

SR래치에서 S=1,R=1일 때 출력이 정의되지 않았었는데, 이러한 상태를 피하기 위해 S와 R의 입력이 동시에 1이 되지 않도록 한 래치이다.

D래치는 이전 SR래치에서 S와 R을 하나로 묶어버리고, 1개의 NOT게이트가 끝단 NAND게이트에 추가로 연결한 모습이다. 따라서 NOT게이트를 통과하면 S,R이 동시에 1이 될 수 없다.

ENABLE단자가 0이면 입력 D에 상관없이 상태유지만 한다.(값 저장)

ENABLE단자가 1이면 동작을 하게 되는데, D = 1이면 Q = 1 으로 SET상태이다.

D = 0이면 Q = 0으로 RESET상태이다.

5.3 플립플롭(Flip-Flop)

플립플롭은 동기식 순차 논리회로에 사용되는 메모리로 1비트의 정보를 저장하는 2진 저장장치이다.

클럭펄스가 발생했을 때 플립플롭에 저장되는 값은 회로의 입력이나 현재 플립플롭에 저장된 값에 의해 결정된다.

클럭펄스가 발생했을 때 플립플롭이 갱신된다. 그러기 위해선 클럭펄스가 발생하기 전 플립플롭의 다음 값을 생성하는 조합논리는 반드시 안정된 상태에 도달해야 한다. 따라서 조합논리회로의 동작속도가 중요하다.

클럭펄스가 규칙적인 간격으로 도달하면 조합논리는 다음 펄스가 도착하기 전에 갱신될 플립플롭의 변화에 응답해야한다.

전송지연은 회로가 정상적으로 동작할 수 있는 클럭펄스의 최소 시간간격을 결정하는 중요한 요소이다.

D래치는 ENABLE이 들어와 있는 한, 입력(D)이 변경되면 출력(Q)의 상태가 변경되여 저장요소로 사용하게 되면 문제가 발생한다. 따라서 ENABLE이 들어와 있을 때 상승(0>1) 혹은 하강(1>0) 에지에서만 트리거되도록 하는 플립플롭을 사용한다.

래치로 D F/F 만드법

Ege trigger D F/F은 가장 적은 수의 게이트로 만든 가장 경제적이고 효율적인 플립플롭이다.

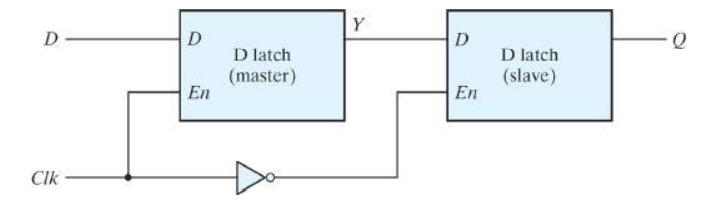

1. D latch 2개 사용 - Master D latch & Slave D latch

D latch 2개가 이어져 있고 clock입력이 앞의 Master D latch에는 그대로, Slave D latch는 NOT게이트를 통과해 들어간다.

따라서 두 latch의 입력이 반대로 들어가므로 Master D latch는 clock이 1일 때 Slave D latch는 clock = 0(clock' = 1)일 때, 즉 clock입력에 따라 번갈아 가며 동작하게 된다.

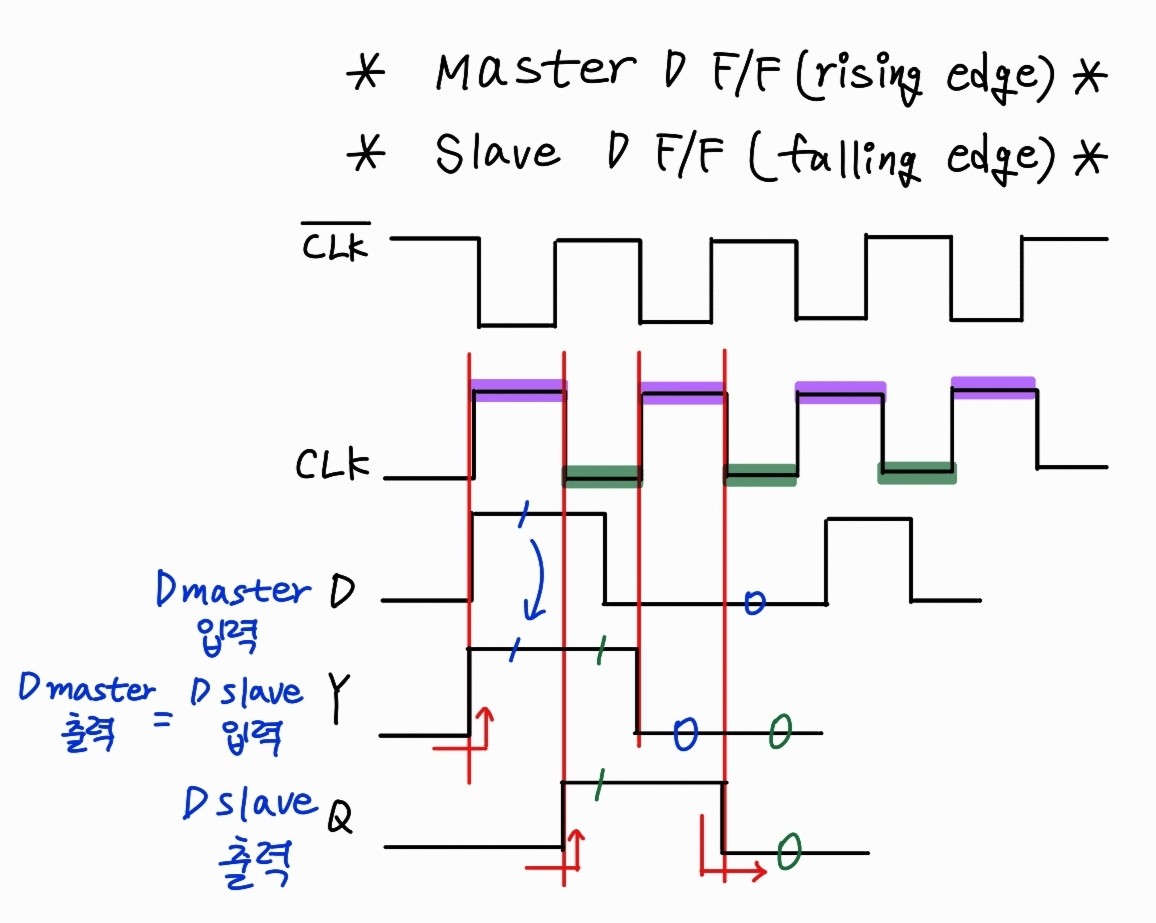

Master D latch는 상승엣지에서 동작하고 Slave D latch는 하강엣지에서 동작한다.

Clock = 1이면 슬레이브 래치는 동작하지 않고 값을 그대로 저장한다. 마스터 래치로 입력 D가 들어와 출력 Y로 전달된다.

Clock이 들어온 상태에서 상승엣지일 때 D가 1이면 Y가 1이 되고, D가 0이면 Y가 0이 된다.

Clock = 0이면 마스터 래치는 동작하지 않고 값을 그대로 저장한다. 슬레이브 래치로 입력 Y가 들어와 출력 Q로 전달된다.Clock이 들어오지 않은 상태에서(clock' = 1) 하강엣지일 때 Y가 1이면 Q가 1이 되고, Y가 0이면 Q가 0이 된다.

따라서 마스터 래치는 클럭이 1이며 상승엣지일 때 동작하고, 슬레이브 래치는 클럭이 0이며 하강엣지일 때 동작한다.

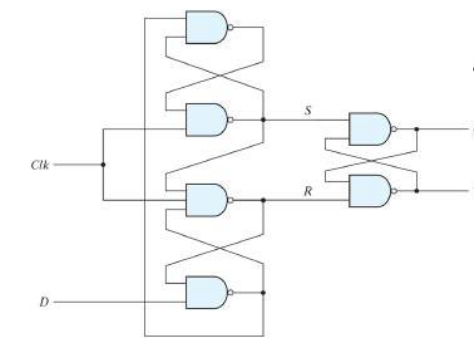

2. S'R'래치 3개 사용

| CLOCK | D | S | R | Q(T+1) |

| 0 | X | 1 | 1 | Q |

| 1 | 0 | 1 | 0 | 0 (SET) |

| 1 | 1 | 1 | 0 | 0 |

| 0 | X | 1 | 1 | Q |

| 1 | 1 | 0 | 1 | 1 (SET) |

| 1 | 0 | 0 | 1 | 1 |

상승엣지 D 플립플롭은 클럭이 들어왔을 때 입력 D값에 따라 D값을 그대로 출력한다.

하강엣지 D 플립플롭은 NOT게이트가 붙어, 클럭이 들어오지 않았을 때 입력 D값에 따라 D값을 그대로 출력한다.

| D | Q(t+1) |

| 0 | 0 (RESET) |

| 1 | 1 (SET) |

이 때 입력의 상태식 D = Q(t+1)

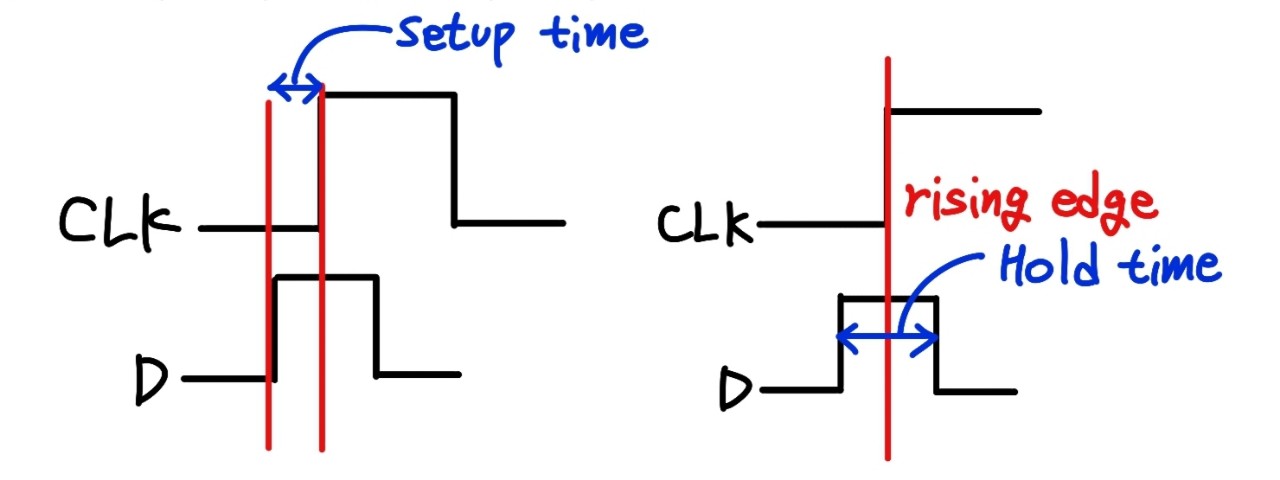

setup time : 클럭천이가 발생하기 전에 입력 D가 일정한 값을 유지해야 하는 최소 시간

hold time : D입력이 클럭의 천이가 일어난 후 변하지 않아야 하는 최소 시간

delay : 트리거 에지가 발생한 순간부터 새로운 상태로 출력이 안정성을 갖게되는 순간

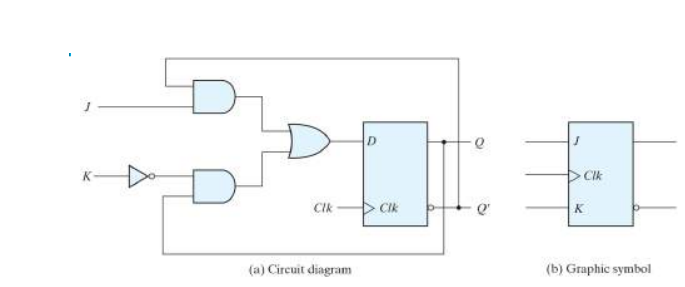

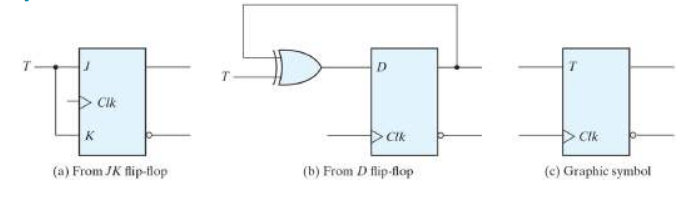

5.4 JK플립플롭

디지털 시스템 설계에서 가장 폭넓게 사용되는 플립플롭은 JK F/F, T F/F이다. JK플립플롭은 D플립플롭과 게이트로 구성된다.

| J | K | Q(t+1) |

| 0 | 0 | Q(t)(상태유지) |

| 1 | 0 | 1 (SET) |

| 0 | 1 | 0 (RESET) |

| 1 | 1 | Q'(t) (Toggle) |

JK플립플롭은 D플립플롭 1개와 OR게이트 1개, AND게이트 2개로 구성되어 있다.

이 때 입력의 상태식 D = JQ' + K'Q이다.

5.5 T 플립플롭

T 플립플롭의 T 는 Toggle을 의미하며 0 을 1로, 1을 0으로 뒤집는다. 즉 보수로 만드는 플립플롭이다.

T 플립플롭은

1. JK플립플롭의 입력단자 J와 K를 하나로 묶은 것과 같다.

2. D 플립플롭의 출력 Q와 T를 XOR 한 것과 같다.

| T | Q(T+1) |

| 0 | Q(t) (상태 유지) |

| 1 | Q'(t) (Toggle) |

이 때 입력의 상태식 D = T⊕Q = TQ' + T'Q

JK F/F, D F/F, T F/F의 특성표와 특성식을 정리하면 다음과 같다.

특성식

D플립플롭 >> D = Q(t+1)

JK플립플롭 >> D = JQ' + K'Q

T플립플롭 >> D = T⊕Q = TQ' + T'Q

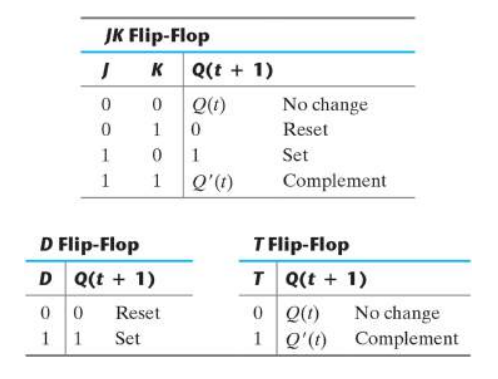

직접입력

클럭과 무관하게 특정한 상태로 변화시키는 비동기 입력

클럭이 작동하기 전에 플립플롭을 시작 상태로 만들 때 유용하다.

1로 세팅 = 직접 SET = PRESET

0으로 세팅 = 직접RESET = CLEAR

요약

SR 래치 > D 래치 > D F/F > JK F/F > T F/F

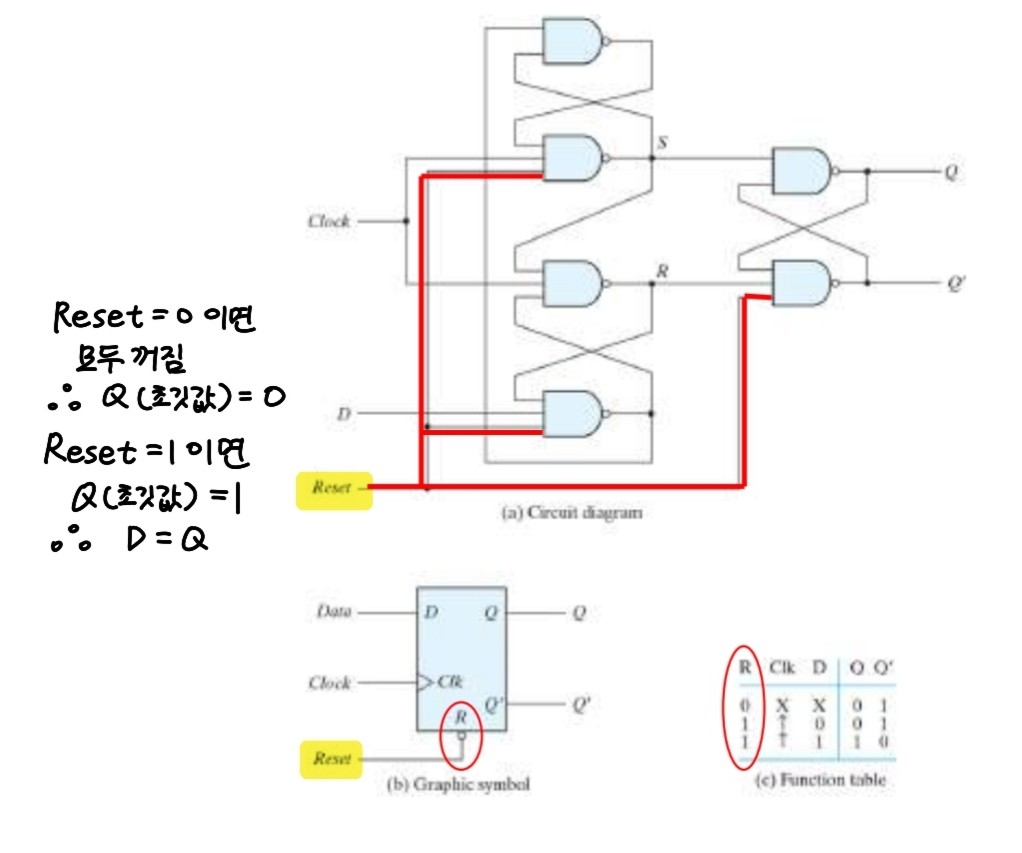

5.6 클럭형 순차 회로 분석(분석 - 상태표)

출력과 다음상태(Q(t+1))는 입력과 현재상태(Q(t))에 의한 함수이다.

상태식(state equation) = 현재상태와 입력들로 다음 상태를 명시함

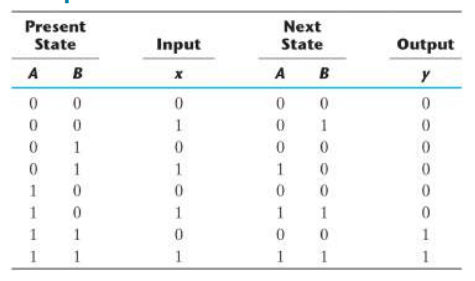

상태표(state table) = 현재상태, 입력, 다음상태, 출력 표기

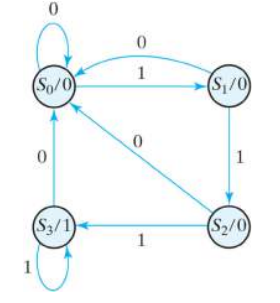

상태도(state diagram) = 상태표를 시각화

순차회로 분석 : 회로도 > 상태식 > 상태표 > 상태도

D플립플롭은 상태식과 다음 상태 값이 일치해서 쉽지만 JK나 T 플립플롭은 다음 상태를 얻기 위해 플립플롭에 따른 특성표와 특성식을 참고해야 한다.

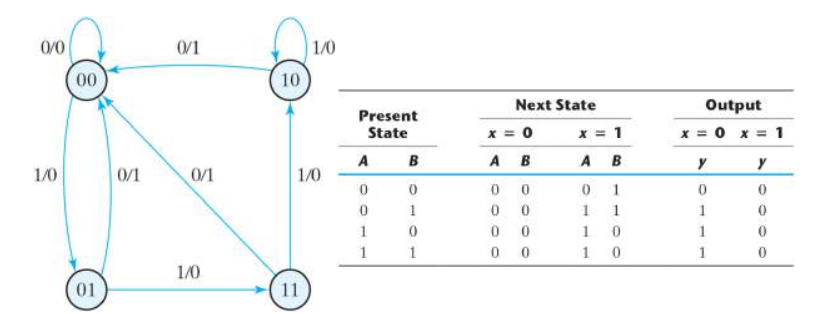

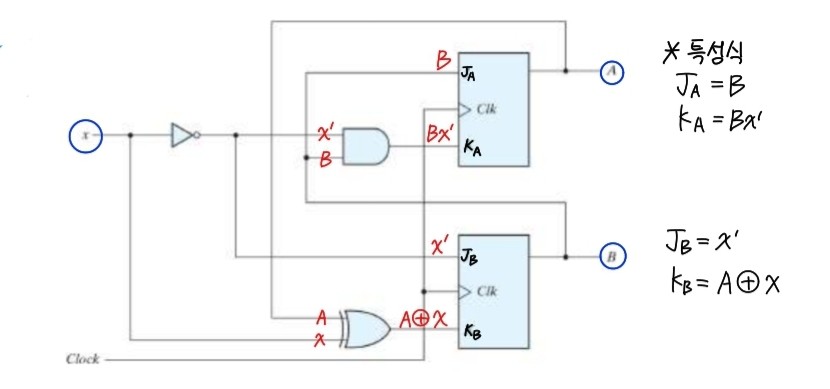

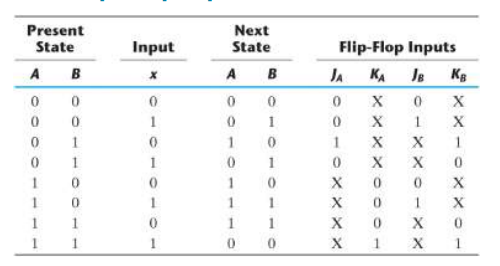

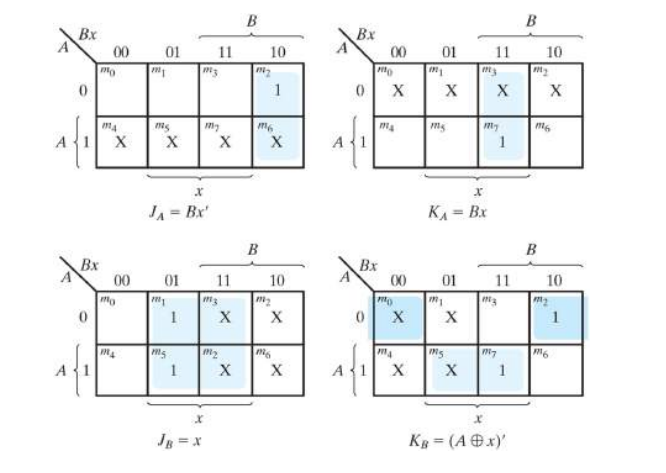

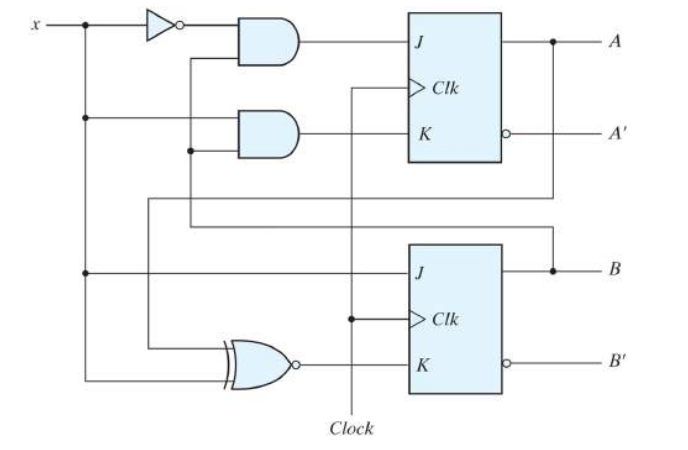

*JK플립플롭을 가진 회로의 분석

특성식 JA = B, KA = BX', JB = X', KB = A⊕X을 구함

입력이 X 1개이고 상태가 2개이므로 플립플롭은 2개 필요하며, 만들 수 있는 조합은 2^2개이다.

특성표를 통해 다음 상태의 상태식을 구하고 상태도를 그리면

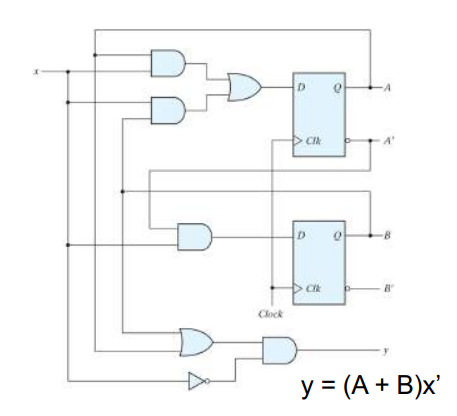

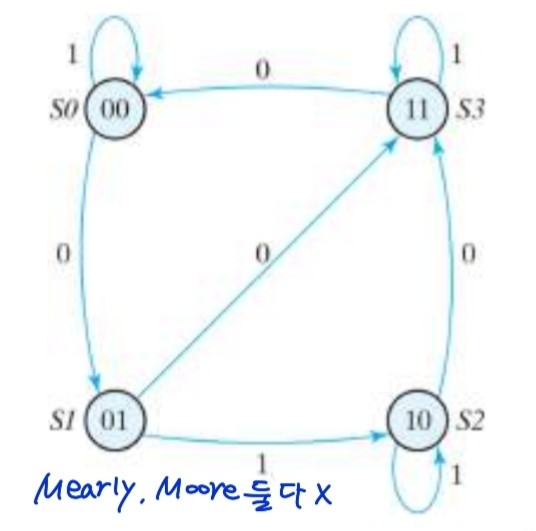

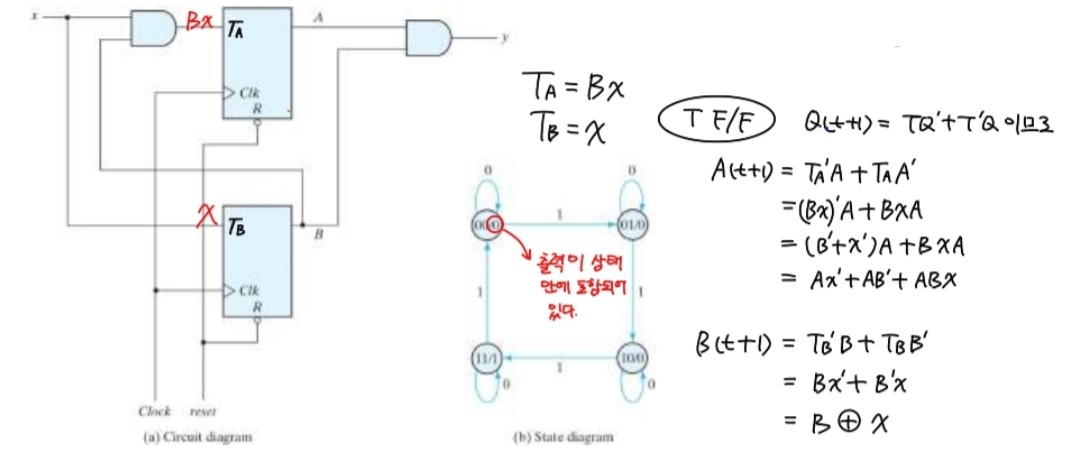

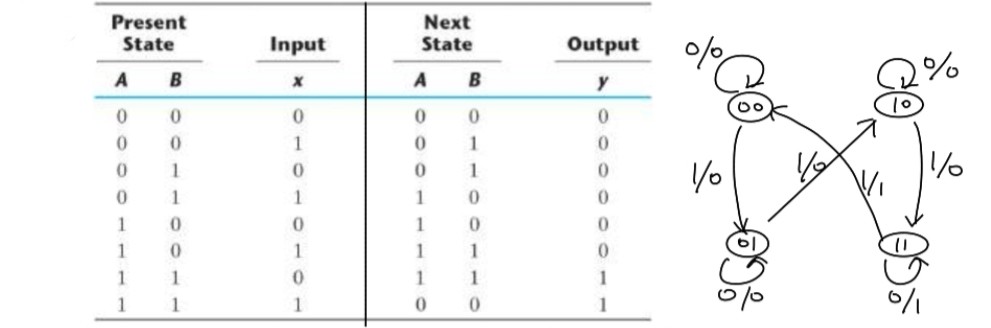

*T플립플롭을 가진 회로의 분석

논리도를 바탕으로 특성식을 구하면 TA = BX, TB = X

입력이 X 1개이고 플립플롭 2개를 사용했기 때문에 만들 수 있는 조합은 2^2개이다.

다음 상태의 상태식은 A(T+1) = AB'+AX'+A'BX, B(T+1) = X⊕B

상태도를 그리면 오른쪽 그림과 같다.

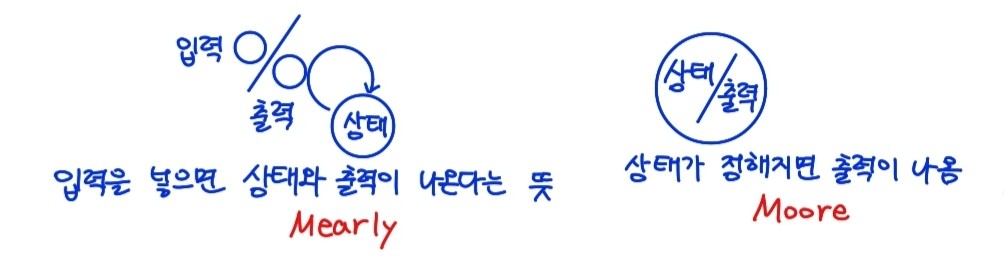

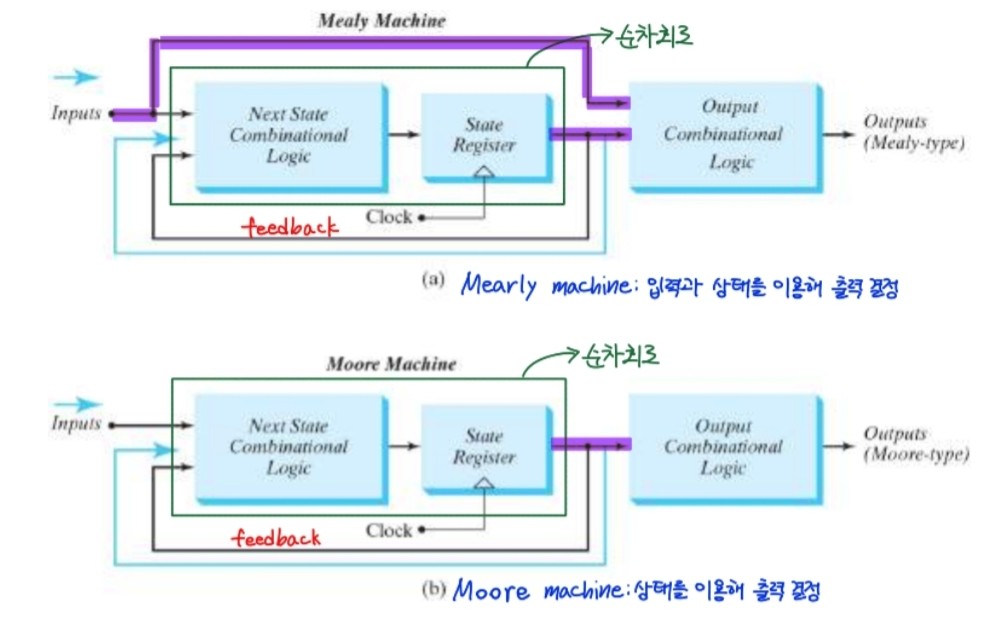

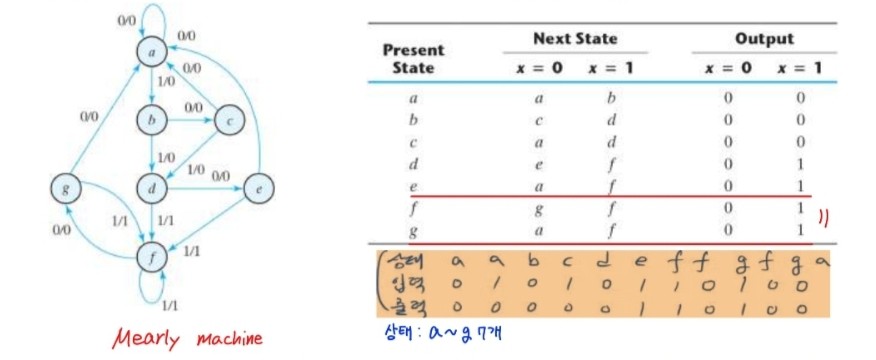

유한 상태머신(finite state machine)의 밀리모델(mearly)과 무어(moore)모델

밀리모델 : 출력이 입력과 현재상태에 관한 함수

밀리모델에서 클럭의 한 주기 동안에 입력이 바뀌면 출력이 바뀔 수 있다.

밀리회로를 동기화 하기 위해선 순차회로의 입력은 클럭과 동기화하고, 출력은 클럭의 활성에지 바로 전의 값으로 한다.

무어모델 : 출력이 현재상태에 관한 함수

무어모델에서 순차회로의 출력은 클럭에 동기화되는 플립플롭의 출력에만 종속적이기 때문에, 순차회로의 출력은 클럭으로 동기화 된다.

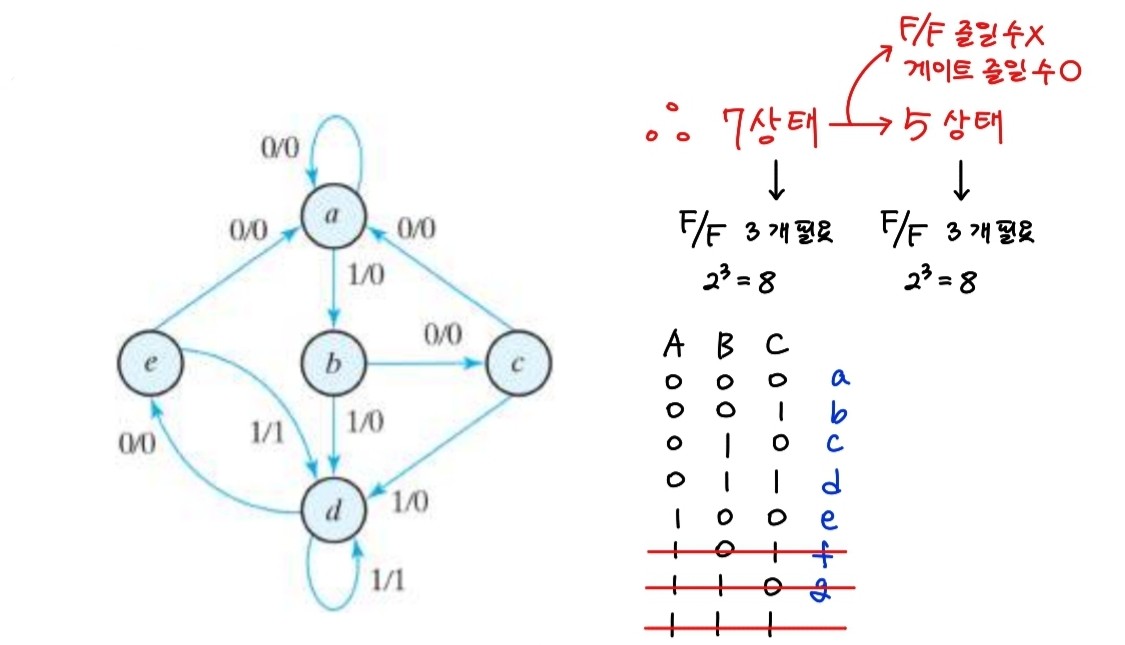

5.8 상태 축소와 할당

상태를 축소하게 되면 플립플롭의 수를 줄일 수 있고 경제적이며 고장률을 줄일 수 있다.

순차회로 분석은 회로도에서 시작해 상태표나 상태도에서 끝난다.

순차회로 설계는 규격들의 집합에서(설계사양) 시작해 논리도로 끝난다.

상태축소 : 플립플롭은 1비트를 저장하는 저장장치이고 상태를 저장한다. 따라서 상태축소는 순차회로의 플립플롭 수를 줄이는 것이다. 다만 플립플롭 수를 줄이면 조합게이트가 더 필요할 수 있다. (플립플롭을 줄이는 것이 더 이득)

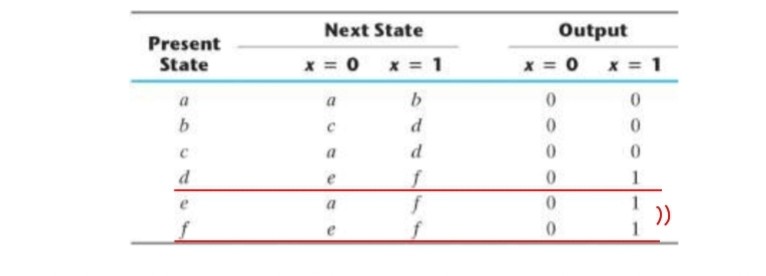

다음 상태표에서 상태는 7개이며 상태 e와 g는 서로 같다. 따라서 g를 삭제하고 g를 모두 e로 변경한다.

상태는 6개이며 상태 d와 f는 서로 같다. 따라서 f를 삭제하고 f를 모두 d로 변경한다.

7상태에서 5상태로 축소된 모습이다.

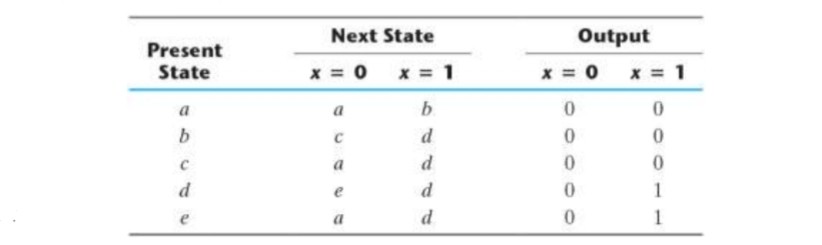

상태 5개를 나타내기 위해선 플립플롭은 3개(2^3=8)가 필요하다.

상태할당 : m개의 상태를 가진 회로는 코드가 2^n >= m 을 만족하도록 n개의 비트를 사용해야 한다.

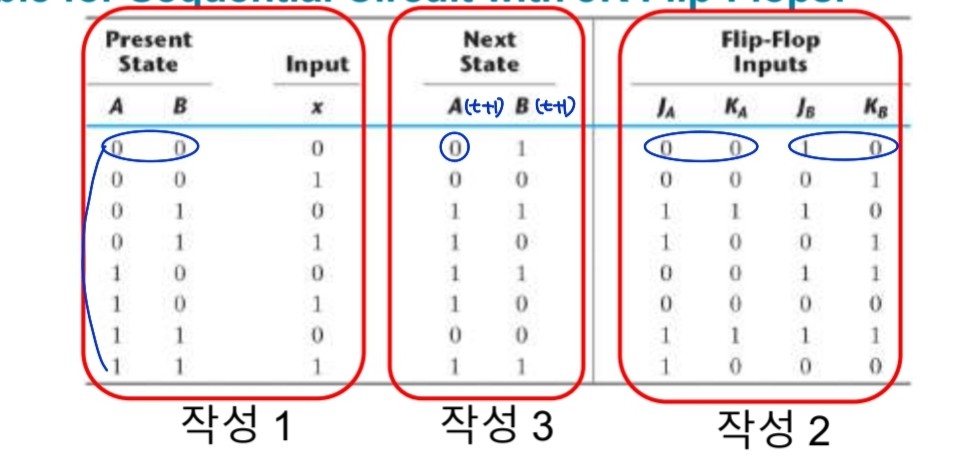

5.9 설계과정(설계 - 여기표)

순차회로 설계과정 : 순차회로는 플립플롭과 조합게이트로 구성된다. 플립플롭 갯수는 상태수와 선택된 상태할당 코드에 의해 결정되고, 조합회로는 플립플롭의 입출력식을 계산해서 얻을 수 있는 상태표에서 유도된다.

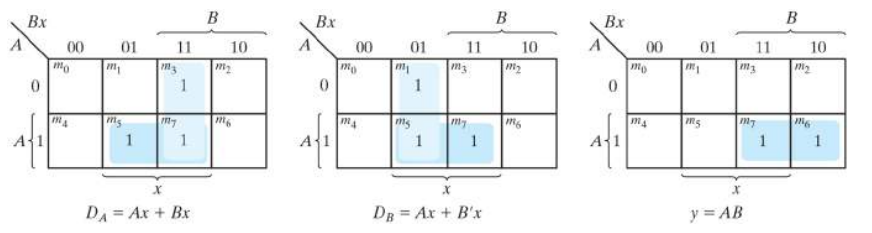

상태도 > 상태표 > k맵에서 입력식 구함 > 논리도

* D플립플롭을 사용한 합성

D플립플롭을 사용한 설계는 플립플롭의 입력을 나타내는 부울 식을 상태표에서 직접 얻을 수 있다.

D플립플롭이 아닌 다른 플립플롭을 이용해 순차 회로를 설계하면 더 복잡해진다. 이 때 여기표를 이용한다.

여기표

* JK플립플롭을 사용한 합성

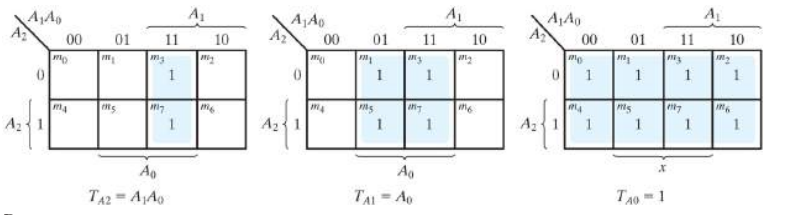

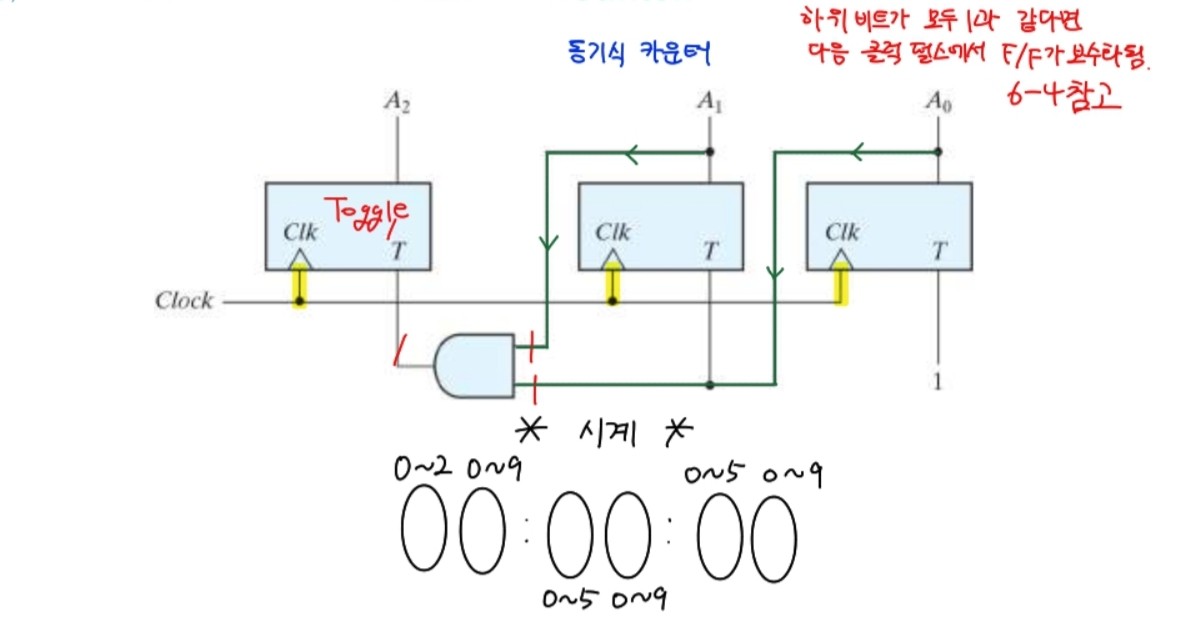

* T플립플롭을 사용한 합성 >> 6-4장 보고 다시 보기

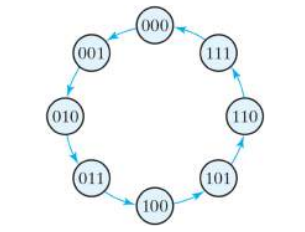

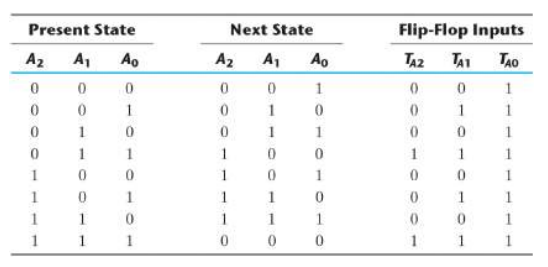

n비트 2진 카운터는 0~(2^n - 1)까지 셀 수 있는 n개의 플립플롭으로 구성된다.

ex) n = 3이면 필요한 플립플롭은 3개, 상태는 8개

000 > 001 > 010 > 011 > 100 > 101 > 110 > 111 > 000 으로 반복된다.

카운터의 상태도는 입력값과 출력값을 나타내지 않는다. 회로의 입력은 클럭 뿐이고 출력값은 플립플롭의 현재 상태이다.

이 성질을 이용하여 디지털 시계를 만들 수 있다.(시간 : 0~23, 분 : 0~59, 초 : 0~59 )

위 3 비트 이진 카운터는 동기식 카운터방식으로 표현한 것으로, 모든 플립플롭이 클럭과 연결되어 있다.

오른쪽부터 왼쪽 순으로 플립플롭이 상위로 가며, 하위비트가 모두 1과 같으면 다음 클럭펄스에서 플립플롭이 AND게이트를 통과해 토글되어 보수화 된다.

위 3비트 이진 카운터는 리플 카운터로도 구현할 수 있다. >> 6장(리플카운터, 이진 카운터)

'논리회로' 카테고리의 다른 글

| [논리회로] 7. 메모리 및 프로그래머블 논리 (0) | 2022.10.24 |

|---|---|

| [논리회로] 6. 레지스터와 카운터 (0) | 2022.10.23 |

| [논리회로] 4. 조합논리 (0) | 2022.10.14 |

| [논리회로] 3. 게이트 레벨 최소화 (0) | 2022.10.12 |

| [논리회로] 2. 부울 대수와 논리 게이트 (0) | 2022.10.10 |