Kim Seon Deok

[Verilog] Sequential modeling - Shift register, Counter 본문

- 순차회로나 래치를 모델링할 땐 always 블록 안에서 nonblocking 할당문을 사용한다.

- 조합회로를 모델링 할 땐 always 블록 안에서 blocking 할당문을 사용한다.

- 동일한 always블록 안에서 blocking 할당문은 순서의 영향을 받기 때문에 blocking 할당문과 nonblocking 할당문을 섞어서 사용하지 않는다.

- 동일한 always 블록에서 순차회로와 조합회로를 구현하려면 nonblocking 할당문을 사용한다.

- 동일한 reg 변수에 값을 할당하게 되면 다수의 여러개의 신호원이 객체에 값을 할당해 multiple source driving 문제가 발생하기 때문에 다수의 always 블록에서 동일한 reg 변수에 값을 할당하지 않는다.

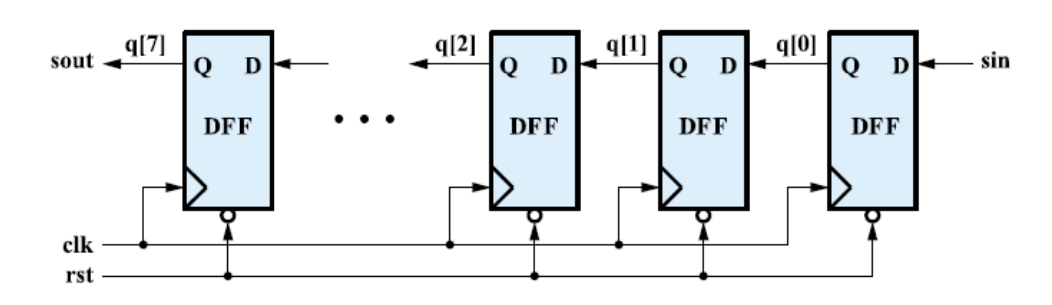

시프트 레지스터(Shift register)

여러 개의 플립플롭이 직렬로 연결된 구조이기 때문에 클럭신호가 인가될 때마다 데이터가 왼쪽 혹은 오른쪽으로 이동하는 회로이다.

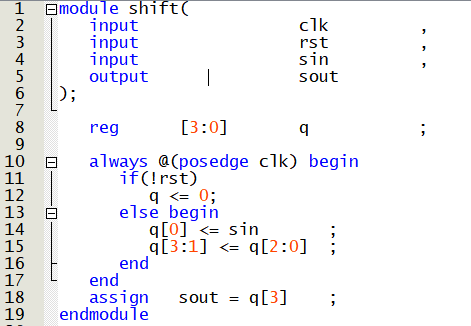

4비트 시프트 레지스터를 구현한 것이다.

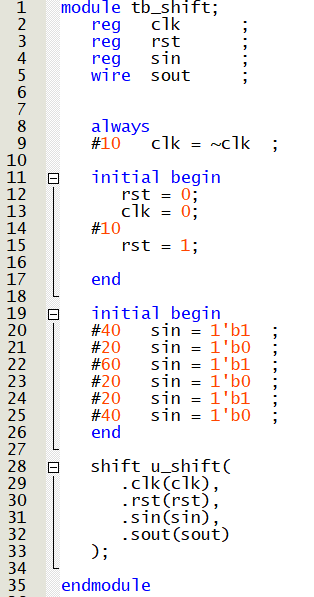

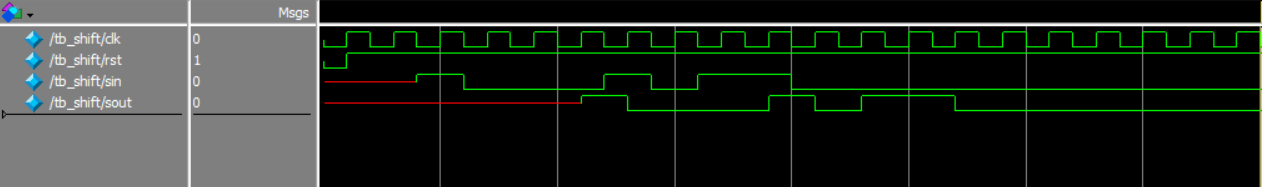

20ns주기로 클럭이 꾸준히 들어오는 상황에서

rst가 0이면 q 값은 0으로 초기화된다.

rst가 1이면 입력값 sin이 q[0]이 되고 q[3:1]은 q[2:0]의 값을 갖는다.

sin은 맨 처음에 unknown인 상태였다가 40ns뒤 값이 1 이 되고

20ns뒤에는 0이 되었다가 60ns뒤에는 1이되고 20ns뒤에는 0이 되었다가 20ns뒤에는 1이 되고 40ns 뒤에는 0이 된다.

4비트시프트 레지스터 이므로 4클럭이 지나고 난 뒤에 sin의 파형을 sout이 갖게 된다.

카운터(Counter)

숫자를 세는 모듈

클럭이 들어올 때마다 값을 증가시키거나 감소시키는 회로이다.

카운터의 이용

1. 메모리 컨트롤러 : 메모리의 원하는 address에 data를 read / write

2. 분주기 : 클럭속도 변화시킴

3. 파이프라인

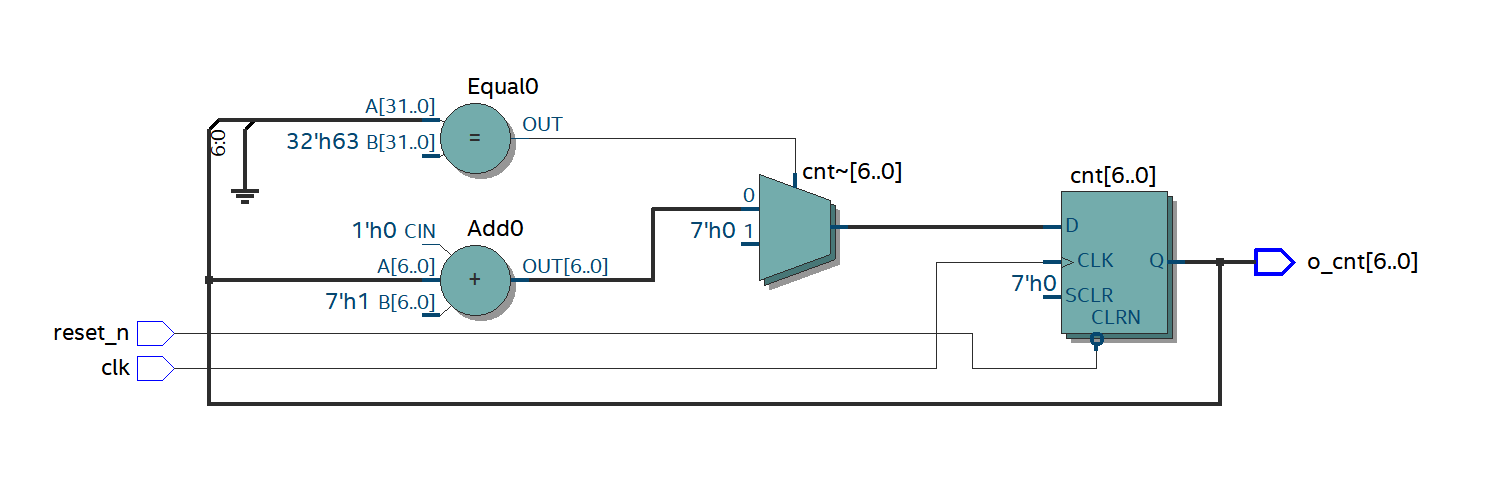

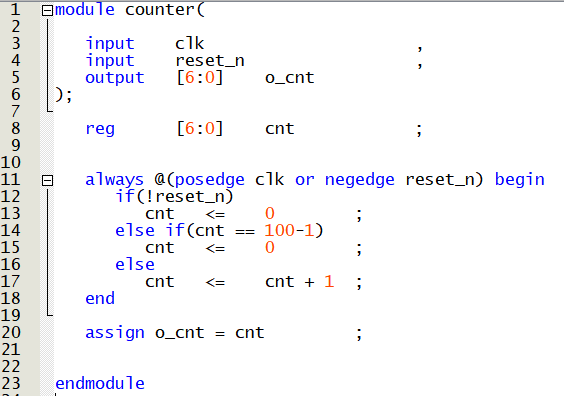

synchronous counter

모든 플립플롭이 하나의 공통 클럭신호에 의해 구동된다.→ 모든 플립플롭의 상태변화가 동시에 일어난다.

장점 : 설계와 검증이 유용하고 카운터 속도가 빠르다.

단점 : 회로가 복잡하다.

asynchronous counter = ripple counter

첫 단의 플립플롭에 클럭신호가 인가되면 플립플롭의 출력이 다음 단의 플립플롭을 트리거 시키는 방식으로 동작한다.

장점 : 회로가 단순하다

단점 : 각 플립플롭의 전파지연시간이 누적되어 최종단의 출력에 나타나기 때문에 카운터 속도가 느리다.

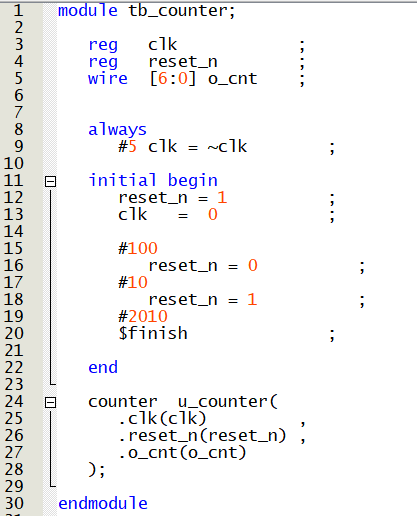

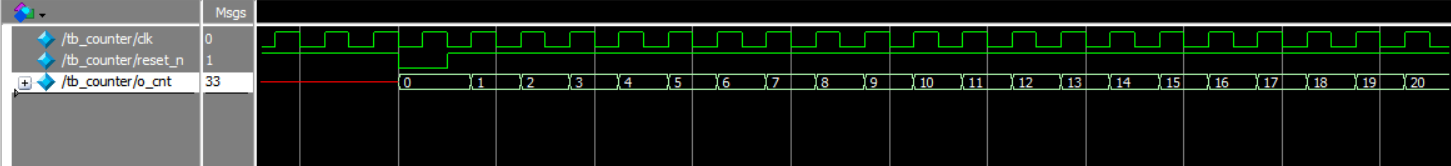

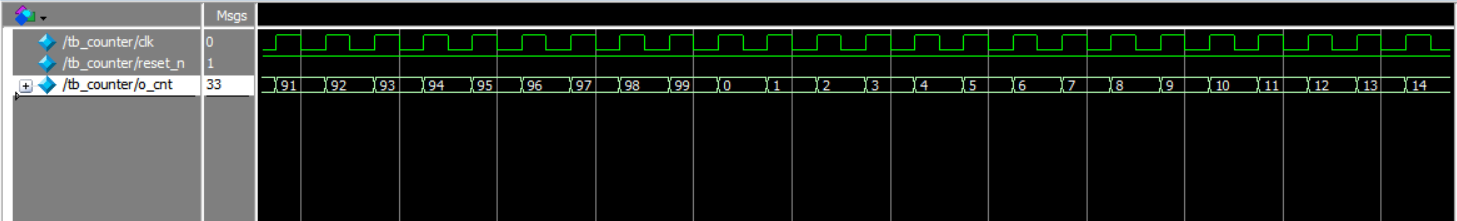

클럭이 10ns주기로 들어오고 있고 맨 처음 o_cnt 값은 unknown상태이다.

reset이 0이 되면 cnt가 0으로 초기화 되고 이후로 reset이 1되면 cnt가 99가 될 때까지 증가하면서 카운트된다.

reset이 1이고 cnt가 99가 되면 cnt는 다시 0으로 초기화 되고 다시 이전 과정을 반복하며 값이 증가한다.

0,1,2,3,4,,,,,,,97,98,99,0,1,2,3,,,,,,97,98,99,0,1,2,3,,,,,,,

'Verilog' 카테고리의 다른 글

| [Verilog] Sequential Logic Modeling - Flip Flop (0) | 2022.12.11 |

|---|---|

| [Verilog] Sequential Logic Modeling - Latch (0) | 2022.12.10 |

| [Verilog] Combinational Logic Modeling (0) | 2022.12.10 |

| [Verilog] Structural modeling - Generate statement (0) | 2022.12.09 |

| [Verilog] Structural modeling - module parameter (0) | 2022.12.09 |