Kim Seon Deok

[Verilog] Sequential Logic Modeling - Latch 본문

조합회로는 현재 들어오는 입력에 의해 출력이 결정된다.

순차회로는 현재의 입력과 과거의 입력, 기억된 상태값에 의해 출력이 결정된다. 과거의 입력과 현재의 상태값을 일정기간 동안 저장하는 기억소자와 조합회로로 구성된다.

ex) register, shift register, counter, 직렬/병령 변환기, 유한 상태머신, 주파수 분주기. 펄스 발생기 등등

순차회로 모델링

always 블록을 이용한 behavioral modeling, gate primitive, module instance, concurrent assign문 등 다양한 베릴로그 구문을 사용한다.

할당문의 형태는 blocking, nonblocking 문에 따라 회로의 동작과 플립플롭의 개수가 달라진다.

래치와 플립플롭은 always 구문 안에 if 조건문을 이용해 모델링하면 되는데, 래치같은 경우 if 문만 있고 else문은 굳이 작성하지 않아 값을 한 클럭 유지시키도록 한다.

래치

래치는 클럭 신호의 0 (negative level sensitive) 또는 1 (positive level sensitive)일 때 동작하는 저장소자이다.

- synchronous

synchronous이면 신호가 클럭신호에 동기화 된 것을 말한다.

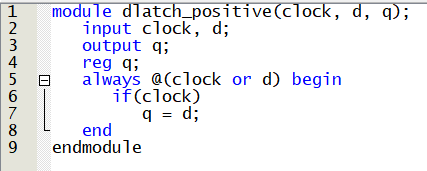

- positive level sensitive D latch

modelsim으로 확인한 결과 다음과 같다.

positive level dlatch의 파형이다.

positive level d latch이므로 clock 파형이 1일 동안만 입력 d값을 따라 q값이 d값으로 변화하고, clock파형이 0일 동안은 그 값을 유지한다. 다시 클럭 값이 1이면 d값에 따라 q 값이 변한다.

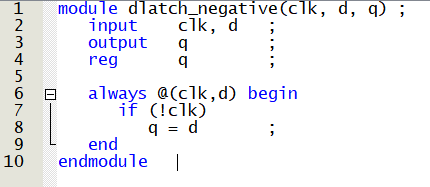

- negative level sensitive D latch

positive level sensitive는 클럭값이 1일 동안 플립플롭이 작동했으니, negative level sensitve는 클럭값이 0일 동안만 플립플롭이 작동하는 것이다.

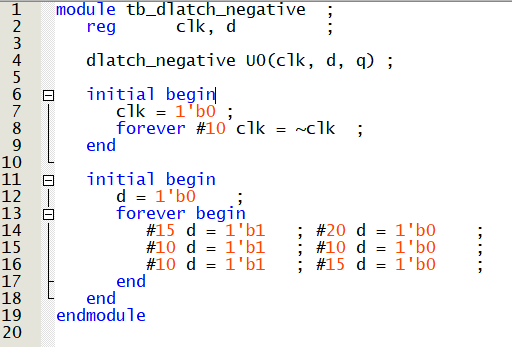

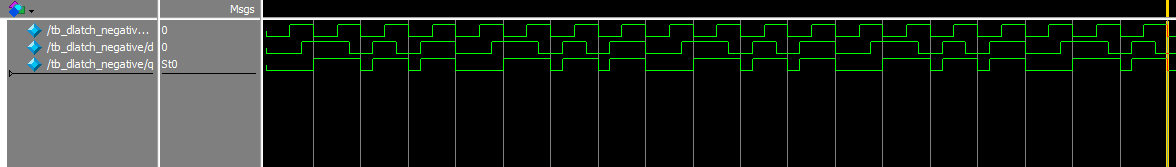

negative level dlatch의 파형이다.

negative level d latch이므로 clock 파형이 0일 동안만 입력 d값을 따라 q값이 d값을 따라 변화하고 clock파형이 1일 동안은 그 값을 유지한다. 다시 클럭값이 0이면 d 값에 따라 q값이 변화한다.

따라서 단순히 if문에 있는 clk 앞에 !를 붙여, clk = 0 인 조건으로 교체해주기만 하면 된다.

2.asynchronous

asynchronous면 set 혹은 reset이 클럭과 동기화 되지 않고 무관하게 출력값을 결정하는 것이다.

set → 래치 값을 1 로

reset → 래치 값을 0 으로

- synchronous active high set/reset

- synchronous active low set/reset

- asynchronous active high set/reset

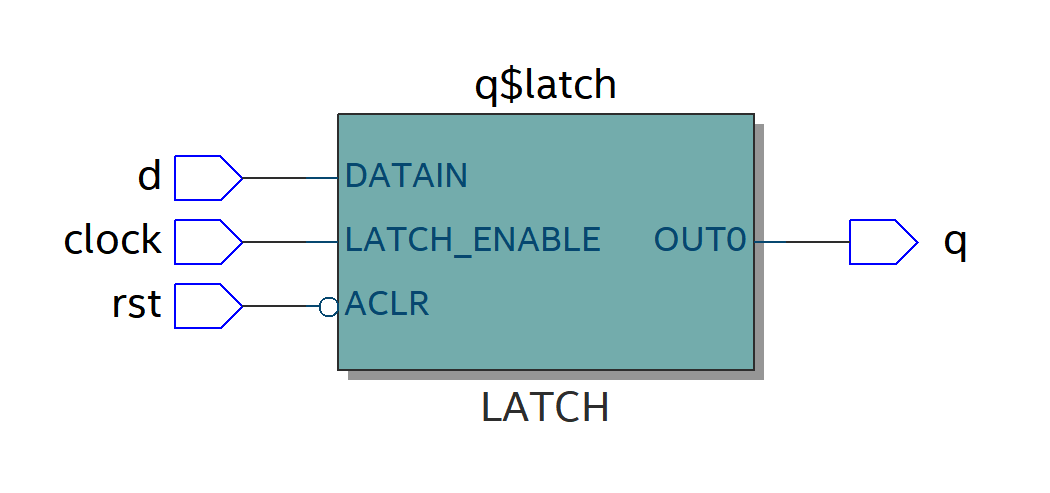

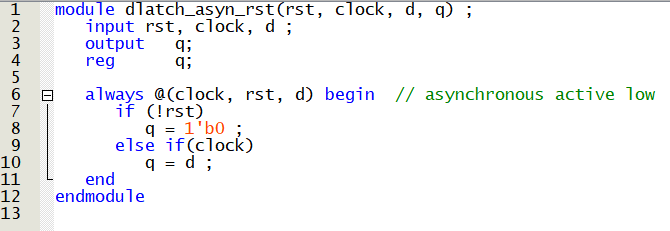

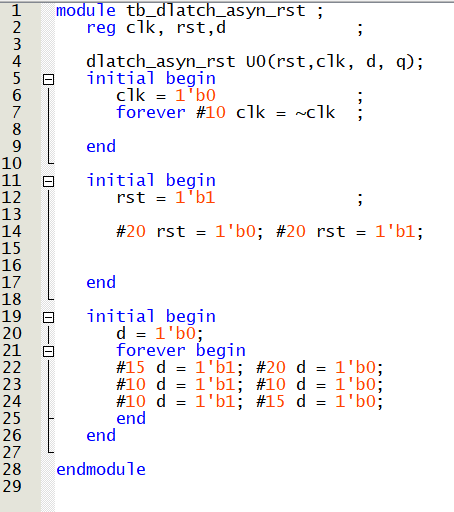

- asynchrounous active low set/reset

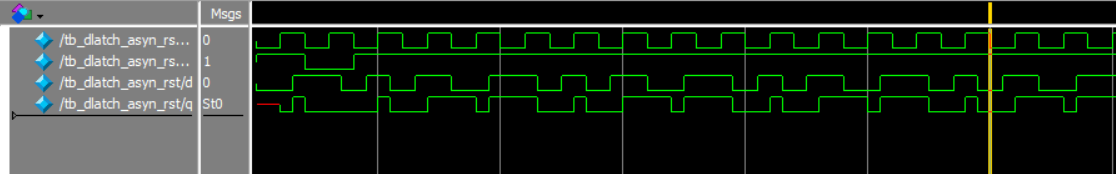

클럭이 10ns만큼 주기적으로 뛰고 있는 상황이다.

positive level d 래치면 클럭이 1일 때 q값이 d값을 따라 바뀐다.

하지만 asynchronous active low rst가 추가되었기 때문에, rst값이 1에서 0이 되면 클럭이 뛰는 것과 상관없이 rst값을 따라 q값이 0으로 바뀐다. 그리고 rst값이 다시 1이 되면 클럭이 1일 때 q값이 d 값을 따라가고 클럭이0이면 q값은 값을 유지한다.

Blocking과 Nonblocking 할당문

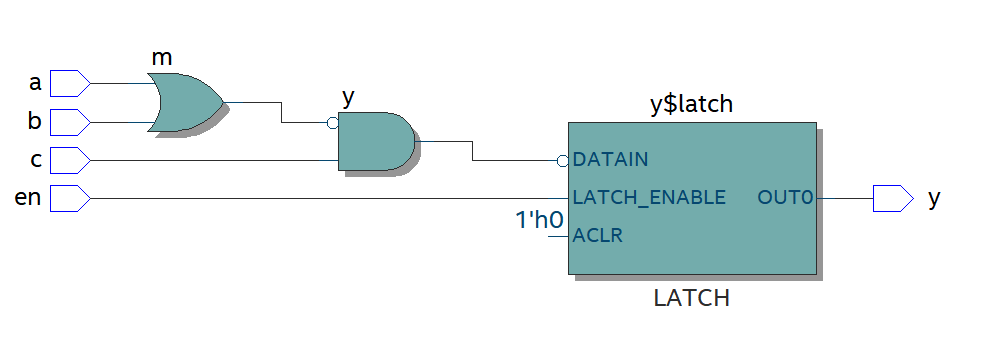

래치가 포함된 회로에 blocking 할당문을 사용

module latch_blk(en, a, b, c, y);

input en, a, b,c ;

output y ;

reg m, y ;

always @(en, a, b, c) begin

if (en) begin // en = 1이면

m = ~(a | b) ; // 다음 줄의 nand gate의 입력으로 들어감

y = ~(m & c) ; // 윗줄 m을 이용

end //else 없으니까 래치 생성

end

endmodule

blocking문을 사용한 경우 if문 내 m값이 다음 y값을 출력을 출력하기 위해 입력으로 사용되기 때문에 플립플롭이 1개만 생성된다.

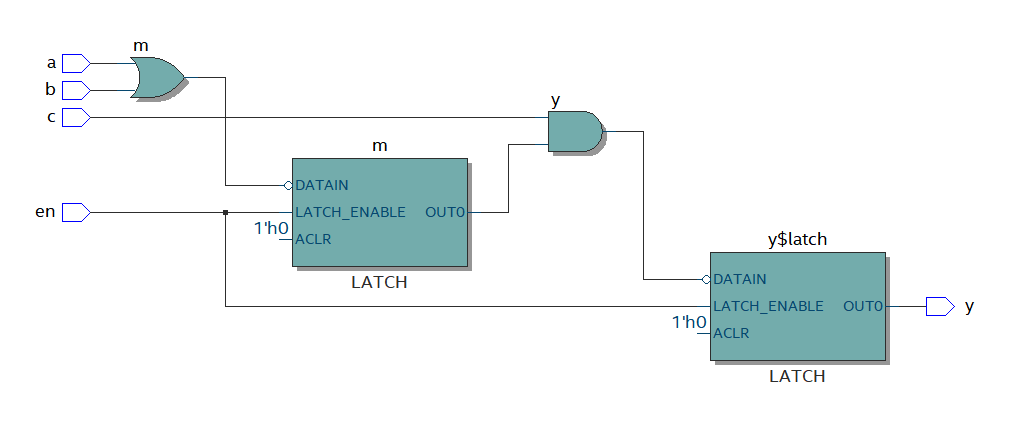

래치가 포함된 회로에 nonblocking 할당문을 사용

module latch_blk(en, a, b, c, y);

input en, a, b,c ;

output y ;

reg m, y ;

always @(en, a, b, c) begin

if (en) begin // en = 1이면

m <= ~(a | b) ; // 우변 동시에 판단

y <= ~(m & c) ; // 이전 클럭주기에서 결정된 m값을 입력으로 함

end //else 없으니까 래치 생성

end

endmodule

nonblocking문을 사용한 경우 우변을 먼저 판단한 다음 좌변에 그 판단한 값을 할당해준다.

따라서 ~(a|b), ~(m&c)를 먼저 판단하고 그 결과값을 m,y에 할당해준다.

이 때 ~(m&c)의 m값은 이전 클럭에서 할당된 m값이다.

따라서 blocking문을 사용하느냐, nonblocking문을 사용하느냐에 따라 플립플롭 개수가 달라지고, 각각의 경우에서 문장의 순서가 바뀐다면 회로도 달라진다.

blocking문 → 문장 순서에 따라 결과적 회로와 래치 개수가 달라질 수 있다.

nonblocking문 → 문장 순서에 상관없이 래치 생성됨. 좌변의 객체는 래치의 출력이 된다.

modelsim 사용법을 까먹어서 참고한 사이트입니다.

쿼터스(Quartus) 및 모델심(ModelSim) 사용법

이번에는 저번 설치 관련 포스트에 이어서 사용하는 방법에 대해서 알려드리고자 합니다. 쿼터스에 모델심 ...

blog.naver.com

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=narabaljeon&logNo=220711700753

Modelsim 사용법 요약본

PDF를 첨부해 놓기는 하였지만 그마져도 보기 귀찮을까봐 필수 요약본만 간추림. 1. 프로젝트를 생성한...

blog.naver.com

'Verilog' 카테고리의 다른 글

| [Verilog] Sequential modeling - Shift register, Counter (0) | 2022.12.11 |

|---|---|

| [Verilog] Sequential Logic Modeling - Flip Flop (0) | 2022.12.11 |

| [Verilog] Combinational Logic Modeling (0) | 2022.12.10 |

| [Verilog] Structural modeling - Generate statement (0) | 2022.12.09 |

| [Verilog] Structural modeling - module parameter (0) | 2022.12.09 |